# UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ

**Colegio de Posgrados**

Modular interface electronic card design for BIMNOV project

# Tesis en torno a una hipótesis o problema de investigación y su contrastación

# Oscar Omar Guilcapi Alulema

# Mr. Martin Cronel, PhD Director de Trabajo de Titulación

Trabajo de titulación de posgrado presentado como requisito para la obtención del título de Máster en Nanoelectrónica

Quito, 06 de enero del 2023

# UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ

# **COLEGIO DE POSGRADOS**

# HOJA DE APROBACIÓN DE TRABAJO DE TITULACIÓN

### Modular interface electronic card design for BIMNOV project

# Oscar Omar Guilcapi Alulema

Nombre del Director del Programa: Título académico: Director del programa de: Luis Miguel Prócel Doctor of Philosophy Maestría en Nanoelectrónica

| Nombre del Decano del colegio Académico: | Eduardo Alba          |

|------------------------------------------|-----------------------|

| Título académico:                        | Doctor of Philosophy  |

| Decano del Colegio:                      | Colegio de Ciencias e |

| Ingenierías                              |                       |

|                                          |                       |

| Nombre del Decano del Colegio de Posgrados: | Hugo Burgos          |

|---------------------------------------------|----------------------|

| Título académico:                           | Doctor of Philosophy |

# © DERECHOS DE AUTOR

Por medio del presente documento certifico que he leído todas las Políticas y Manuales de la Universidad San Francisco de Quito USFQ, incluyendo la Política de Propiedad Intelectual USFQ, y estoy de acuerdo con su contenido, por lo que los derechos de propiedad intelectual del presente trabajo quedan sujetos a lo dispuesto en esas Políticas.

Asimismo, autorizo a la USFQ para que realice la digitalización y publicación de este trabajo en el repositorio virtual, de conformidad a lo dispuesto en la Ley Orgánica de Educación Superior del Ecuador.

Nombre del estudiante:

Oscar Omar Guilcapi Alulema

Código de estudiante:

00215379

C.I.:

1722538020

Lugar y fecha:

Quito, 06 de enero del 2023

# ACLARACIÓN PARA PUBLICACIÓN

**Nota:** El presente trabajo, en su totalidad o cualquiera de sus partes, no debe ser considerado como una publicación, incluso a pesar de estar disponible sin restricciones a través de un repositorio institucional. Esta declaración se alinea con las prácticas y recomendaciones presentadas por el Committee on Publication Ethics COPE descritas por Barbour et al. (2017) Discussion document on best practice for issues around theses publishing, disponible en http://bit.ly/COPETheses.

# **UNPUBLISHED DOCUMENT**

**Note:** The following graduation project is available through Universidad San Francisco de Quito USFQ institutional repository. Nonetheless, this project – in whole or in part – should not be considered a publication. This statement follows the recommendations presented by the Committee on Publication Ethics COPE described by Barbour et al. (2017) Discussion document on best practice for issues around theses publishing available on http://bit.ly/COPETheses.

# DEDICATORIA

A mis padres Roberto y Nelly, y a mi hermano Bryan por todo el apoyo durante el transcurso de este posgrado

Oscar Omar

#### ACKNOWLEDGMENTS

I would like to thank to all people that contributed to the development of this master's degree. I would like to thank Mr. Luis Miguel Prócel the nanoelectronics' master director at USFQ and all teachers I found during the formation. To my classmates, friends and people who I spend time with during the all-academic and non-academic activities during this period. I would like to thank Mr. Adam, Quotb the ESECA master director at ENSEEIHT where I spent the second year of this formation.

I would like to thank my internship supervisor Mr. Martin Cronel for all support and guidance during this project. Furthermore, I would like to thank Mr. Ioav Ramos and Mr. Kaviraj Baboulal for all help and advice provided in this project.

I am also thankful to NOVATEM Society and all its member's staff for the opportunity to let me develop my last semester there.

To conclude, I thank my family for all the unconditional support in this academic year.

#### 1. RESUMEN

Cada producto que NOVATEM diseña y construye debe ser sometido a pruebas para asegurar los requerimientos, en este momento, para probar las soluciones desarrolladas, NOVATEM también diseña pequeños prototipos con los cuales se pueden hacer los ensayos. Evidentemente, cada nuevo producto implica obligatoriamente desarrollar la fase de construcción del prototipo para el ensayo lo cual consume recursos y requiere de grandes cantidades de tiempo de diseño.

BIMNOV tiene por objetivo eliminar esta fase, se plantea como una solución modular en la cual el banco de ensayos estará totalmente listo. Para lograr ésta modularidad, una tarjeta madre será concebida como el núcleo central del proyecto donde muchas otras tarjetas electrónicas podrán ser conectadas de acuerdo a los requerimientos del dispositivo bajo prueba.

Es así que BIMNOV contendrá todos los módulos necesarios y arquitecturas para la etapa de pruebas y validación de los principales productos y nuevos desarrollados por NOVATEM. Será suficiente conectar e intercambiar las tarjetas módulo de acuerdo con el tamaño del dispositivo bajo pruebas, en tipo de señales a ser medidas y la información a ser recolectada.

BIMNOV también tiene una visión de escalabilidad en la cuál si una nueva tarjeta modular es desarrollada, esta pasará a formar parte del catálogo disponible y podrá ser utilizada para pruebas futuras.

La principal contribución al proyecto BIMNOV fue desarrollar una solución capaz de identificar las tarjetas módulo que son conectadas en la tarjeta madre, cada tarjeta depende del tipo de dispositivo mecatrónico bajo prueba. Para realizar esta conceptualización se debe identificar los componentes, tipos de señales y protocolos de comunicación que serán utilizados, todo esto se detalla en las siguientes secciones

#### 2. ABSTRACT

Every product that NOVATEM designs, and builds must be tested to ensure the requirements, at this stage, to test the developed solutions NOVATEM uses to also design small prototypes to carry on the essays with. Evidently, each new product implies mandatory the development of this prototype building phase, which consumes resources and demands large amounts of designing time. BINMOV focuses on eliminating this stage, it is proposed as a modular solution where the test bench will be already set. To achieve this modularity a motherboard will be conceived as the heart of the project where several card modules can be plugged in according to the requirements of the tested device.

Therefore, BINMOV will contain all necessary modules and architectures for the testing and validation stage of the principal and new products of NOVATEM. It will be enough to connect and exchange the card modules according to the size of the device under test and the type of signals to be measured and information to be gathered. BINMOV also envisages the scalability where if a new card module is developed for a special device, this module will form part of the available modules catalog and will be used in for future test.

The main contribution to BINMOV project was to conceptualize a solution capable of identifying several card modules which are plugged into a motherboard, in general, each card module corresponds to a sensor, actuator, monitor or control signal that depends on the type and size of the final mechatronic device under test. To achieve this conceptualization, it was indispensable first to identify the available hardware and software that we will be using for, to know which type of signals we will work with, to determine the protocol of communication and to design the electronics that will perform the identification tasks. Next sections summarize the principal tasks performed during the internship.

### CONTENTS

| 1. | RE        | SUMEN                                                                                                     | 7    |

|----|-----------|-----------------------------------------------------------------------------------------------------------|------|

| 2. | AB        | STRACT                                                                                                    | 8    |

| 3. | INT       | TRODUCTION                                                                                                | . 14 |

|    | 3.1       | The Company                                                                                               | . 15 |

|    | 3.2       | Presentation of services                                                                                  | . 16 |

|    | 3.3       | NOVATEM Team                                                                                              | . 17 |

|    | 3.4       | The project BINMOV                                                                                        | . 18 |

|    | 3.5       | State of the Project                                                                                      | . 20 |

| 4. | LIT       | ERATURE REVIEW                                                                                            | . 22 |

| 4  | 4.1       | Hardware and Software Characterization                                                                    | . 22 |

|    | I/O       | 333-6 Multifunction I/O Mezzanine Module                                                                  | . 24 |

|    | IO        | 35 Analog and Digital I/O module                                                                          | . 26 |

| 4  | 4.2       | Signals Assignation/Identification                                                                        | . 29 |

| 4  | 4.3       | Selection of the communication protocol.                                                                  | . 32 |

|    | Inte      | er-Integrated Circuit Protocol - I2C                                                                      | . 32 |

|    | Ser       | ial Peripheral Interface - SPI                                                                            | . 34 |

| 5. | RE        | SEARCH METHODOLOGY AND DESIGN                                                                             | . 37 |

|    | 5.1       | Card Identification                                                                                       | . 37 |

| 6. | PR        | OPOSED SOLUTIONS FOR CARD IDENTIFICATION                                                                  |      |

|    | 5.1       | Analog Solutions                                                                                          | . 40 |

|    | 6.1       | 1 Voltage Divider                                                                                         | . 40 |

|    | 6.1       | 2 Voltage reference                                                                                       | . 43 |

|    | 5.2       | Digital Solutions                                                                                         | . 45 |

|    | 6.2<br>mo | .1 Solution 1: 8 TCA9555 Chip Implementation – Until 16 modules on th therboard                           |      |

|    | 6.2<br>mo | 2 Solution 2 – 6 TCA9555 and 2 TCA6424A combination – Until 18 dules on the motherboard                   | . 52 |

|    | 6.2<br>Un | .3 Solution 3 – MAXIM7311 2-Wire-Interfaced 16-Bit I/O Port Expander<br>til 64 modules on the motherboard |      |

| 7. | RE<br>56  | AD/WRITE 64 SELECTABLE DIFFERENT ADDRESSES TEST MODUL                                                     | Æ    |

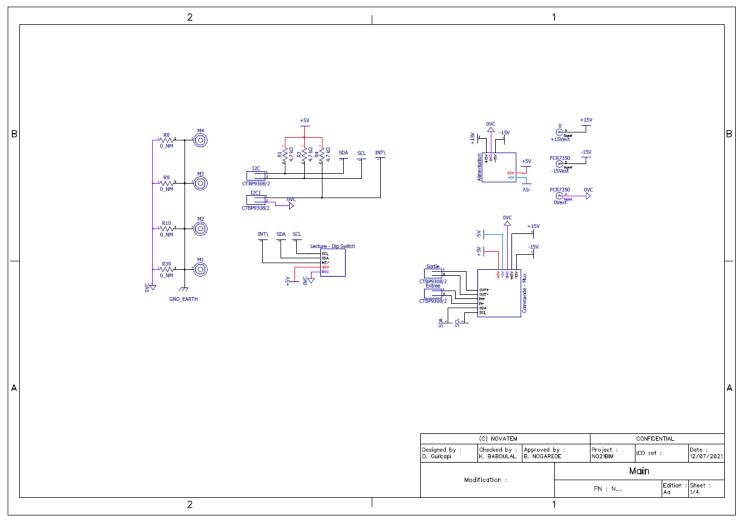

| ,  | 7.1       | Design                                                                                                    | . 56 |

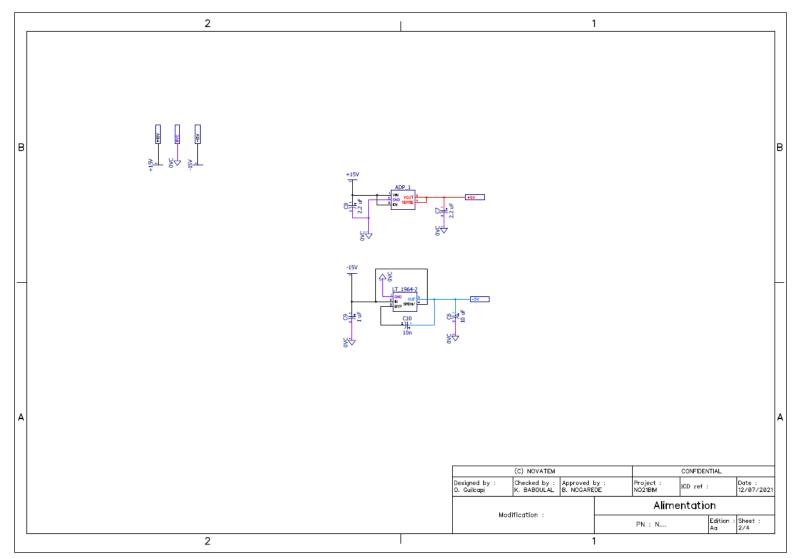

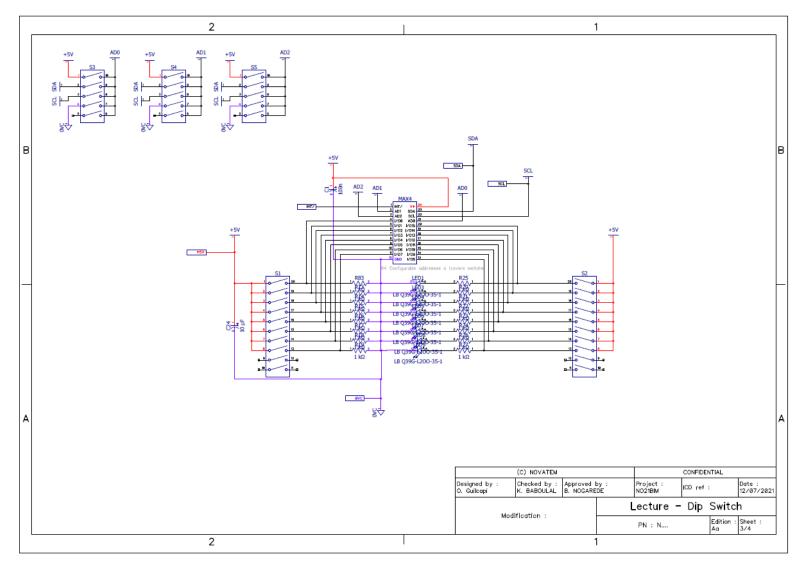

|    | 7.1       | 1 Read Module                                                                                             | . 59 |

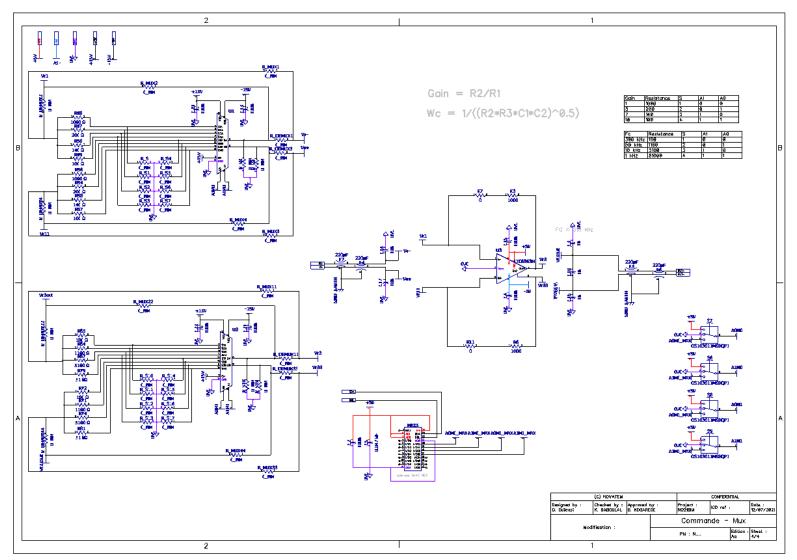

|    | 7.1       | 2 Write Module                                                                                            | . 60 |

| ,  | 7.2       | PCB Creation                                                                                              | . 64 |

| 8.  | DATA ANALYSIS                          | 69 |

|-----|----------------------------------------|----|

| 8.  | 1 Testing                              | 69 |

| 8.2 | 2 Multiplexer Testing                  | 69 |

| 8.3 | 3 I2C Testing                          |    |

| 9.  | ACQUIRED COMPETENCES – AUTO EVALUATION |    |

| 10. | GENERAL CONCLUSION                     |    |

| 11. | REFERENCES                             |    |

| 12. | ANNEXES INDEX                          |    |

|     |                                        |    |

### TABLE INDEX

| Table 1. NOVATEM services                                           |    |

|---------------------------------------------------------------------|----|

| Table 2. NOVATEM staff                                              |    |

| Table 3. Communication protocols                                    |    |

| Table 4. ADC Electrical interface                                   |    |

| Table 5. DAC Electrical interface                                   |    |

| Table 6. Digital I/O and P14 Rear I/O Electrical Interface          |    |

| <b>Table 7.</b> Extrait of signals going from Speedgoat to the Bay. |    |

| Table 8. Extrait of signals going from the Bay to Speedgoat.        |    |

| Table 9. I2C Main characteristics                                   |    |

| Table 10. SPI main characteristics.                                 |    |

| Table 11. I2C vs SPI                                                |    |

| Table 12. I2C Address selection                                     | 41 |

| Table 13. R2 values when R1 is fixed                                |    |

| Table 14. Address Reference                                         | 47 |

| Table 15. Address Reference                                         |    |

| Table 16. Extrait MAX7311 Address Map                               | 55 |

| Table 17. Gain and cutoff frequency values                          |    |

### **FIGURES INDEX**

| 1. At he left - NEXGED project for Latécoère, electric piloting of an aircraft |                                                                                                |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|                                                                                |                                                                                                |

|                                                                                |                                                                                                |

|                                                                                |                                                                                                |

| 4. Hardware-in-the-loop representation                                         | 22                                                                                             |

| 5. Performance real-time target machine                                        | 23                                                                                             |

| 6. Plug-In Concept                                                             |                                                                                                |

| 7. IO135 Block diagram.                                                        | 26                                                                                             |

| 8. Inter-Integrated Circuit (I2C) Protocol.                                    | 32                                                                                             |

| 9. I2C message frame                                                           |                                                                                                |

| <b>10.</b> Serial Peripheral Interface (SPI) protocol.                         | 35                                                                                             |

| 11. BINMOV's Motherboard and Card Modules representation                       | 39                                                                                             |

| <b>12.</b> TLA2528 Application                                                 | 40                                                                                             |

| 13. TLA2528 Block Diagram                                                      | 41                                                                                             |

| 14. Voltage Stabilizer Circuit using a Buffer                                  | 42                                                                                             |

| 15. Shunt Regulator Schematic                                                  | 43                                                                                             |

| <b>16.</b> TCA955 Chip general description                                     | 46                                                                                             |

| <b>17.</b> TCA9555 Address                                                     | 47                                                                                             |

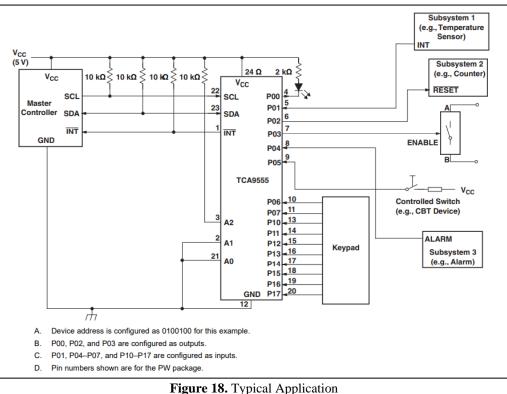

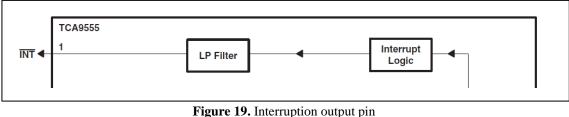

| <b>18.</b> Typical Application                                                 | 48                                                                                             |

| <b>19.</b> Interruption output pin                                             | 49                                                                                             |

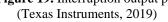

| <b>20.</b> Solution 1: 8 TCA9555 Chip Implementation with interruption line    | 51                                                                                             |

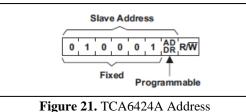

| 21. TCA6424A Address                                                           |                                                                                                |

| <b>22.</b> Solution 2 – 6 TCA9555 and 2 TCA6424A combination                   | 53                                                                                             |

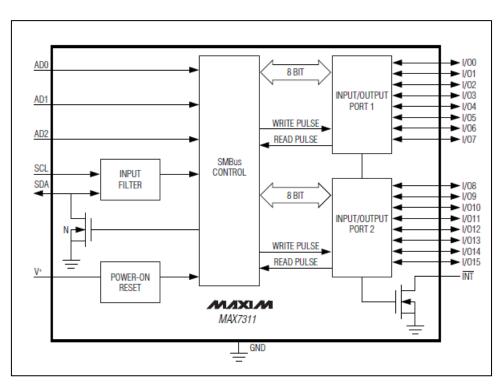

| 23. MAX7311 Block Diagram                                                      | 54                                                                                             |

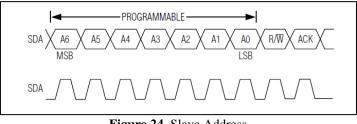

| 24. Slave Address                                                              |                                                                                                |

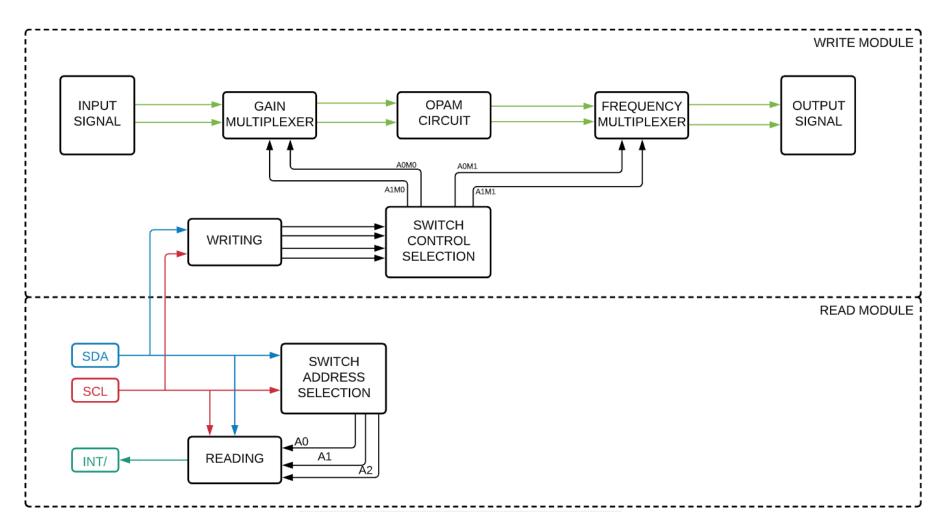

| 25. Test Module Block Diagram                                                  | 58                                                                                             |

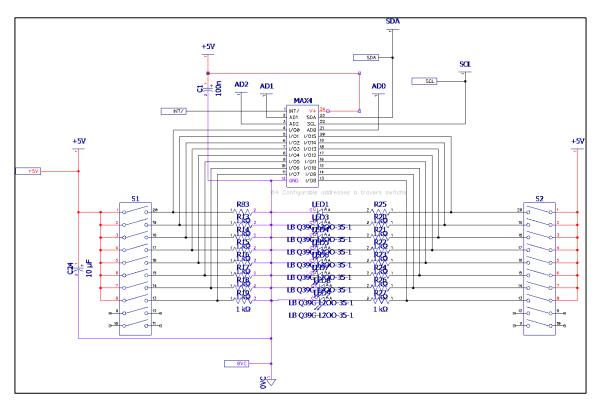

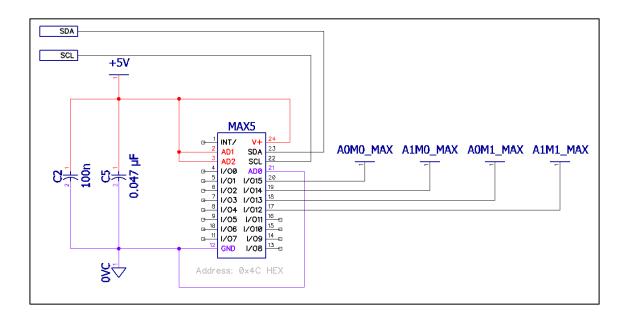

| <b>26.</b> Read Module - MAX7311                                               | 59                                                                                             |

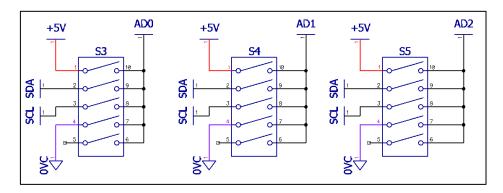

| 27. Read Module - Switch address selection                                     | 60                                                                                             |

| 28. Write Module - MAX7311 MUX outputs                                         | 60                                                                                             |

| <b>29.</b> Second order Rauch structure                                        | 61                                                                                             |

| <b>30.</b> Circuit Model of Basic Discrete PGA                                 | 62                                                                                             |

| <b>31.</b> ADG 1409 implementation for gain selection.                         | 63                                                                                             |

| <b>32.</b> Selection control mode switches                                     | 63                                                                                             |

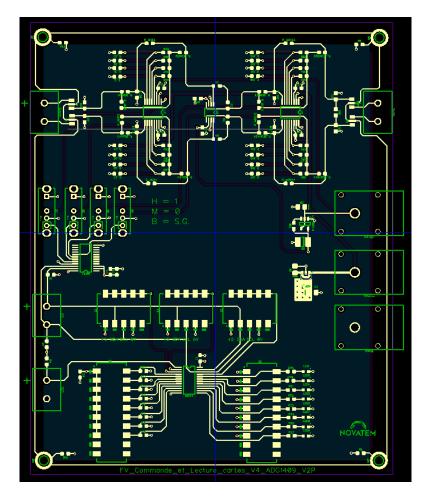

| <b>33.</b> PCB Top view                                                        | 64                                                                                             |

| <b>34.</b> PCB Bottom view                                                     | 65                                                                                             |

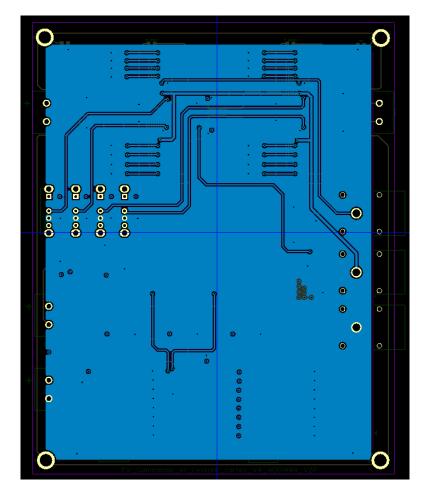

| <b>35.</b> Real PCB                                                            | 66                                                                                             |

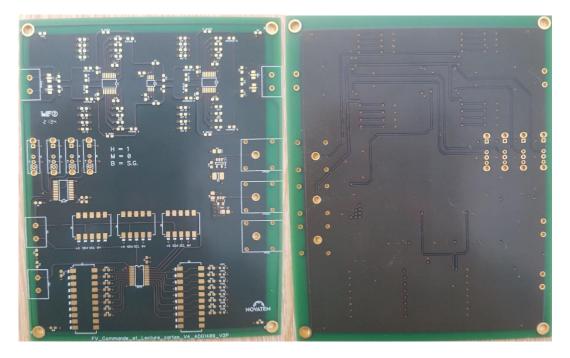

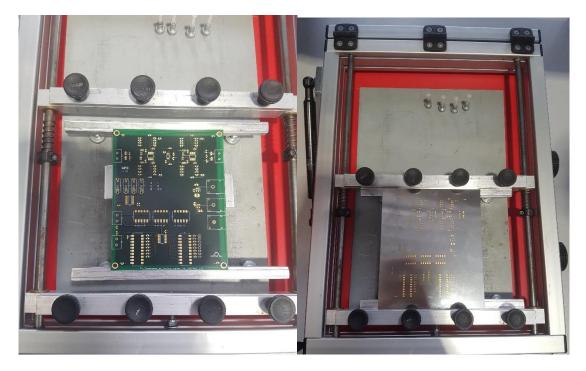

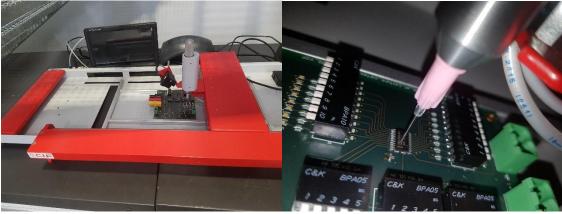

| <b>36.</b> TECPRINT 500                                                        | 66                                                                                             |

| <b>37.</b> Components Placement                                                | 67                                                                                             |

| <b>38.</b> Reflow oven                                                         | 67                                                                                             |

| <b>39.</b> Final PCB module                                                    | 68                                                                                             |

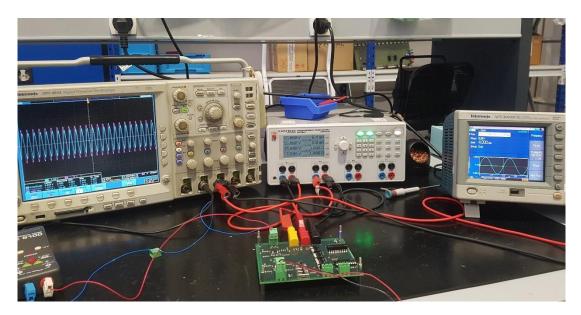

| <b>40.</b> Multiplexer testing equipment                                       | 69                                                                                             |

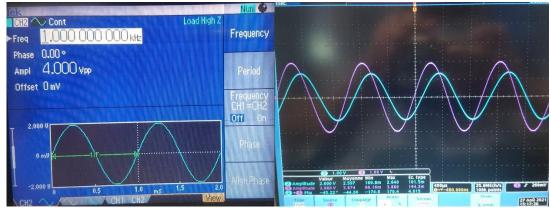

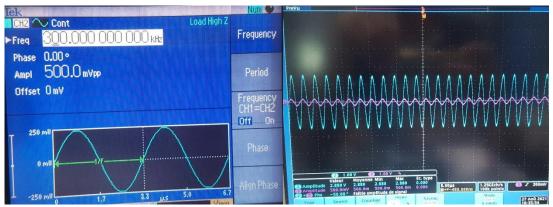

| 41. Waveforms for input and output signal when Vin pk-pk=4[V] at f=1 [kHz]     | ].                                                                                             |

|                                                                                |                                                                                                |

| 42. Waveforms for input and output signal when Vin pk-pk=1[V] at f=10 [kH:     |                                                                                                |

|                                                                                |                                                                                                |

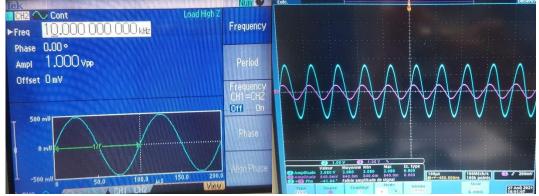

| <b>43.</b> Waveforms for input and output signal when Vin pk-pk=0.7[V] at f=50 |                                                                                                |

|                                                                                | 71                                                                                             |

|                                                                                | <ul> <li>2. BINMOV's general architecture.</li> <li>3. BINMOV's Spatial distribution</li></ul> |

| Figure 44. Waveforms for input and output signal when Vin pk-pk=0.5[V] at f=3 | 00 |

|-------------------------------------------------------------------------------|----|

| [kHz]                                                                         | 71 |

| Figure 45. Test protocol extrait                                              | 72 |

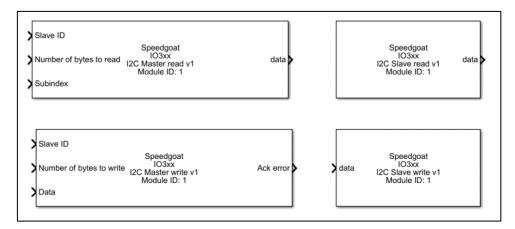

| Figure 46. I2C Speedgoat Simulink Blocks                                      | 72 |

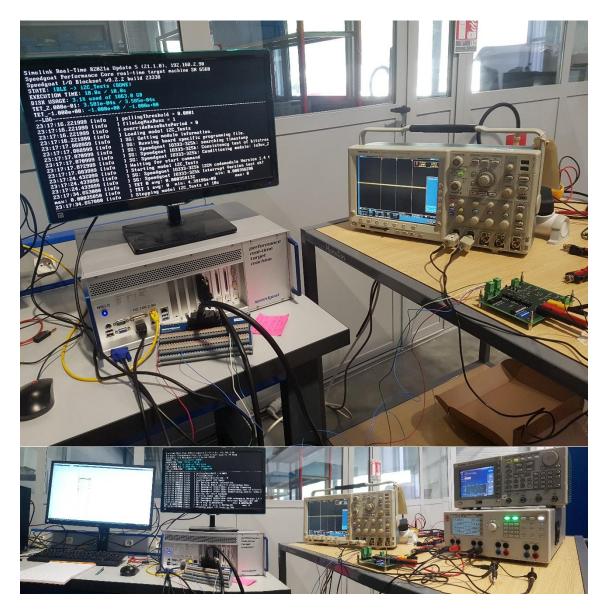

| Figure 47. I2C Testing assembly                                               | 73 |

|                                                                               |    |

#### **3. INTRODUCTION**

BINMOV is a project from NOVATEM society, it is pretended to be a test bench module that will help he company to reduce time when testing new developed devices.

The main characteristic of BINMOV is its modularity, it consists of a series of card modules that are plugged in a motherboard, they can be changed according to the type and size of the mechatronic system being tested so that if a new system should be tested it will be enough to connect a card according to the new device characteristics to perform a complete test. In this way the time is drastically reduced since the test bench module is ready and there is no need to create additional subsystems to test the main device.

During the internship I worked in conceptualizing a solution that allows the identification of each card, this identifier permits to know which card is being used and in which position is in the motherboard. The cards are different purposes modules, for instance, a card to measure the current of a motor, another to measure the voltage of a brake or the temperature of an engine. Therefore, with this identification system one can know both the measured variable and to which mechatronic device the transmitted electronic signal corresponds to.

BINMOV relays in the implementation of this card modules together with Speedgoat, a real-time target machine, that executes the routine test. This machine offers several I/O ports, PWM channels, single-ended and differential analog ports, and different communication protocols.

This document exposes how the identification task was accomplished first by understanding the available hardware characteristics, proposing different analog and digital solutions according to the requirements and finally by validating the design trough a PCB prototype.

#### 3.1 The Company

NOVATEM SAS is an enterprise created in 2007 by Mr. Bertrand NOGAREDE, doctor, researcher, and former professor at engineering school ENSEEIHT in the field of electrical engineering specializing in electrodynamics.

NOVATEM deals with the design, sizing, manufacturing, and production of electric actuators combining electromechanics, electromagnetism, electrodynamics, and in general, electrical engineering.

The company acts in several fields of activity due to the versatility of its solutions such as: aeronautics, space, automobile, medicine, nuclear, naval

The dynamism of NOVATEM has allowed to collaborate and manage projects from numerous partners such as AIRBUS, SAFRAN, NAVAL GROUP, FINE HEART (Figure 1).

The company is present into two sites, a Production & Head office center in Coursan near Narbonne and a Research & Engineering center in Toulouse.

Figure 1. At he left - NEXGED project for Latécoère, electric piloting of an aircraft door. At the right - Powerful electric motor developed by Novatem. (NOVATEM SA, 2020)

# 3.2 Presentation of services

| <b>NOVATEM</b><br>Recherche  | <ul> <li>High performance mechatronic integration</li> <li>Reliability &amp; Availability of electromagnetic converters</li> <li>High frequency electromagnetic machines</li> </ul>                                                                                                                                                          |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>NOVATEM</b><br>Ingénierie | <ul> <li>Establishment of specifications according to demand</li> <li>Study and calculate the sizing of mechanical, electromechanical, and electronic parts</li> <li>Perform a multitude of simulations in order to have the best possible results</li> <li>Develop a manufacturing file containing the different characteristics</li> </ul> |

| <b>NOVATEM</b><br>Production | <ul> <li>of the products (design, plan, power, etc.)</li> <li>Perform the tests of the mechatronics assembly on a test bench, suitable for the latter</li> <li>Test bench</li> <li>Electronic card</li> </ul>                                                                                                                                |

|                              | Active part                                                                                                                                                                                                                                                                                                                                  |

Table 1. NOVATEM services

#### 3.3 **NOVATEM Team**

| Ioav RAMOS        | Engineer doctor<br>Head of the design office                                   |  |

|-------------------|--------------------------------------------------------------------------------|--|

| Bertrand NOGAREDE | Doctor of Electrical Engineering - Electrodynamics<br>Manager of NOVATEM       |  |

| Reda ABDOUH       | Electromechanical engineer<br>Calculation Engineer                             |  |

| Maxime NOMDEDEU   | Mechatronics technician<br>Responsible for production and technical assistance |  |

| Martin CRONEL     | Engineer doctor in industrial computing<br>Industrial IT and control engineer  |  |

| Magali TRESSOL    | ICA Auditor<br>Quality manager, administrative                                 |  |

| Alexandre GIRAUD  | Engineer doctor<br>Post-doctoral researcher                                    |  |

|                   | Diploma                                                                        |  |

Table 2. NOVATEM staff

Position in charge

Coursan site

Toulouse site

#### 3.4 The project BINMOV

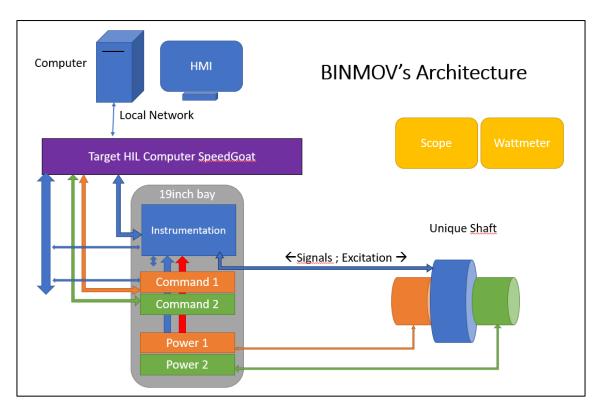

The BIMNOV project – Baies d'Interface Mécatronique NOVATEM (in french) – NOVATEM Mechatronic Interface Racks – aims to equip the company with a mean of testing, interfacing, and controlling mechatronic systems. Its main characteristics are its modularity and long-term availability. This structure (Figure 2) should make it possible to control and characterize mechatronic assemblies of various architectures.

The envisaged modularity is based on several aspects:

- The type of assembly under test:

- Permanent magnet machine.

- Induction machine.

- <sup>D</sup> MRV (variable reluctance machines) with limited number of phases.

- <sup>D</sup> Linear actuator based on the three machines above.

- Zero current brake.

- Controllable magnetic coupler.

- Power electronics.

- The ability to switch easily between:

- <sup>D</sup> Behavioral simulation based on models.

- Real-time simulation of a mechatronic assembly.

- <sup>D</sup> Mechatronic assembly control (RCP philosophy).

- HIL simulation.

- The electronics of the bench that can be replaced by electronics under test with or without a mechatronic assembly.

The MBD philosophy, coupled with those of HIL and RPC, will allow the analytically simulated modules to be interchanged with those physically simulated, but also with hardware modules. This makes it possible, for example, to reduce the risk of errors being introduced during development or to make functions more easily according to the specifications. This new process also intrinsically makes it possible to reduce the time to market while increasing the operating safety of the assemblies.

Some of the electronic modules developed specifically for instrumentation will complete a fundamental research project on the intrinsic ferromagnetic qualities of materials intended for the manufacture of electrical machines. In addition, other modules will collect data intended for understanding the operation of a switching cell, precisely at the switching scale.

From an industrial research point of view, BIMNOV will allow the development of safe operating architectures, making it possible to place the functions as close as possible to the mechatronic assemblies while simulating them at the highest level of the developed system.

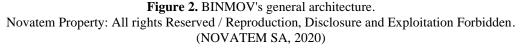

Figure 3. BINMOV's Spatial distribution Novatem Property: All rights Reserved / Reproduction, Disclosure and Exploitation Forbidden. (NOVATEM SA, 2020)

The BIMNOV project therefore represents a double stake for the company, firstly as an extension of its own test resources, while constituting a significant opportunity to expand its commercial offer in the direction of the marketing of a modular and scalable test and characterization tool for its customers (NOVATEM SA, 2020).

#### **3.5** State of the Project

When I was integrated in the project, the architecture, the modules that BINMOV owns and the general planning of the project had already been defined. How the tasks were going to be divided, the equipment required and necessary time to complete each stage were also defined, however the design work itself was just starting.

At that date BINMOV had an approximate advance of 40%. During the development of the internship the design part was attacked, especially the electronic and programming part. In these 6 months, several work teams including 2 interns participated

in the design of signal acquisition circuits, signal conditioning, filters, control and communication circuits.

By the time I am writing this report, it is estimated that BINMOV is at 65 %, in the coming months the functional tests will begin, and it is expected to achieve the 1.0 BINMOV version by the end of the year.

#### 4. LITERATURE REVIEW

#### 4.1 Hardware and Software Characterization

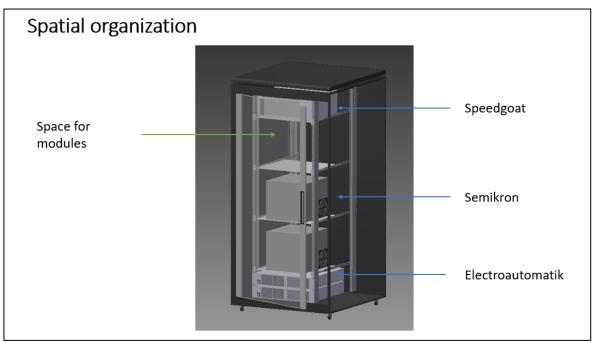

NOVATEM tests its developed devices employing the Hardware-in-the-loop methodology (Figure 4), HIL testing allows simulate sensors, actuators, and mechanical components in a way that all inputs/outputs of the device under test are connected long before the final system is integrated, this approach relays on the use of representative real-time responses, electrical stimuli and functional use cases (Add2, 2021).

Figure 4. Hardware-in-the-loop representation (Add2, 2021)

The modeling environment used by NOVATEM is Simulink where the plant models are created. This environment is run on a workstation, the host PC, and then the plant simulation is compiled into real-time executable code, which is downloaded to a second computer, called the target simulator. This simulator is a specialized hardware device which contains special I/O boards and all required signal conditioning (Add2, 2021).

SPEEDGOAT is hardware device used to perform the HIL simulations, specifically the "Performance real-time target machine" model (Figure 5) is employed in NOVATEM, this device has a vast range of I/O connectivity and supports industrial protocols, ideal for multi-FPGA solutions requiring MHz closed-loop bandwidths and hundreds of I/O (Speedgoat, 2021).

Figure 5. Performance real-time target machine (Speedgoat, 2021)

This machine is equipped with modules that provides digital LVCMOS I/O lines, differential and common mode analog lines, PWM output lines, communication protocols interface, and interruption ports. They constitute a suitable interface for signal conditioning, converting voltage levels and shielding by adding protection against voltage shifting.

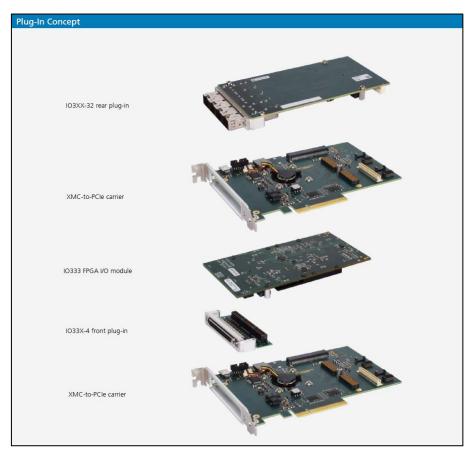

These modules are built in a plug-in concept which allows connect many modules depending on the application requirements (Figure 6). Specifically, the modules that will be used in BINMOV are the IO135-Performance, the IO333-325K-Performance, the

IO333-6-Performance and the IO333-21-Performance A briefly description concerning the electronic main characteristics, voltage levels and samples rates is presented in next sections.

Figure 6. Plug-In Concept (Speedgoat, 2020)

### I/O333-6 Multifunction I/O Mezzanine Module

### Input

### High Speed Analog Input

16-bit Analog to Digital Converter (ADC) channels provide simultaneous sampling at a maximum rate of 500 kHz.

#### Programmable Input Voltage Range

Four gain selections are available that allow a bipolar input voltage range from  $\pm$

1.28 Volts to  $\pm$  10.24 Volts.

#### Output

#### Analog Output

Eight 16-bit Digital to Analog Converter (DAC) channels provide simultaneous update with a maximum rate of 100 KHz.

#### Programmable Output Voltage Range

Three gain selections are available that allow a bipolar output voltage range from  $\pm 10$  Volts to  $\pm 10.5263$  Volts (Acromag Inc., 2013).

#### Communication

The modules front IO333-6 and rear IO333-21 integrate also a 1x SPI Master/Slave (TTL), 1x I2C Master (TTL), 16x PWM (TTL), 1x Interrupt (TTL) channels.

| Pin | Code<br>Module<br>Channel | Functionality   | Direction | Transceiver |

|-----|---------------------------|-----------------|-----------|-------------|

| 1   |                           | Ground          |           |             |

| 2   | 1                         | SPI - CLK       | IN/OUT    | TTL         |

| 3   | 1                         | SPI - CS        | IN/OUT    | TTL         |

| 4   | 1                         | SPI - SDO       | OUT       | TTL         |

| 5   | 1                         | SPI - SDI       | IN        | TTL         |

| 61  | 1                         | I2C Master CLK  | OUT       | ΠL          |

| 62  | 1                         | I2C Master Data | IN/OUT    | ΠL          |

(Speedgoat, 2021)

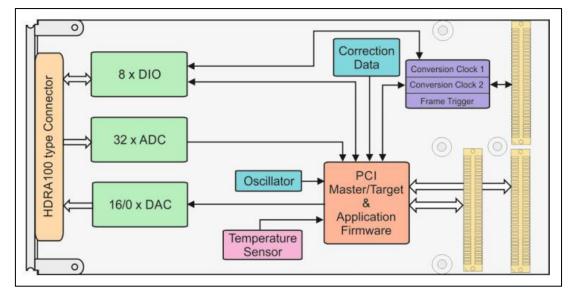

#### IO135 Analog and Digital I/O module

The Speedgoat IO135 module is a standard single-wide PCI Mezzanine Card (PMC)

Figure 7. IO135 Block diagram. (Speedgoat, 2018)

#### Input

- The IO135 module provide 32 true differential analog input channels (ADC Channels) avail-able at the Front I/O Connector.

- AD7609 from Analog Devices is used for the analog inputs. Each AD7609 provides eight 16-bit differential ADC channels (ADC Channels A-H).

- The IO135 module provide four AD7609s (ADC1, ADC2, ADC3 & ADC4), resulting in 32 analog input channels (Speedgoat, 2018).

- The ADCs offer true differential inputs with software selectable ±5V and ±10V bipolar input voltage ranges (one common setting for all eight channels of each ADC).

• The maximum sample rate of the ADCs is 200kSPS and they offer an oversampling capability with a digital filter (Speedgoat, 2018).

| Protection                           | 7kV ESD rating<br>±16.5V Overvoltage Clamp Protection |

|--------------------------------------|-------------------------------------------------------|

| Input Type                           | True bipolar differential                             |

| Input Impedance                      | 1ΜΩ                                                   |

| Input Capacitance                    | 5pF                                                   |

| Maximum Ground-Related Input Voltage | ±5∀ and ±10∀                                          |

| Full Scale Range                     | ±10∨ and ±20∨                                         |

| Common-Mode Input Range              | ±4V                                                   |

| Sample Rate                          | 200kSPS                                               |

| (Speedgoat, | 2018) |

|-------------|-------|

|-------------|-------|

#### Output

- The IO135 module provides up to 16 analog output channels (DAC Channels) available at the Front I/O Connector

- AD5754R from Analog Devices is used for the analog outputs. Each AD5754R provides four 16-bit single-ended DAC channels (DAC Channels A-D).

- The IO135 module provides four AD5754Rs (DAC1, DAC2, DAC3 & DAC4), resulting in 16 analog output channels (Speedgoat, 2018).

- The DACs offer software selectable 0-5V, 0-10V, 0-10.8V, ±5V, ±10V and ±10.8V output voltage ranges (individual setting for each of the four channels of each DAC).

The settling time is typically 10µs and the DAC channels can drive a load of 2kΩ, with a capacitance up to 4000pF (Speedgoat, 2018).

| Protection            | 3.5kV ESD rating                                       |  |

|-----------------------|--------------------------------------------------------|--|

|                       | 20mA current limit                                     |  |

| Output Type           | unipolar/bipolar single-ended                          |  |

| Output Voltage Ranges | $\pm$ 5V, $\pm$ 10V, $\pm$ 10,8V, +5V, +10V and +10.8V |  |

| DC Output Impedance   | 0.5Ω                                                   |  |

| Maximum Load          | 2kΩ                                                    |  |

| Capacitive Load       | 4000pF                                                 |  |

| Settling Time         | 10µs                                                   |  |

Table 5. DAC Electrical interface

(Speedgoat, 2018)

In case of a DAC Channel overcurrent condition, the DAC Channel is powered down and its output is clamped to ground with a resistance of  $\sim 4k\Omega$ .

#### **Digital I/O**

Each of the 8 Digital I/O lines on the Front I/O connector and each of the Global Conversion Signals on the P14 Rear I/O are realized by separated input and output buffers with a  $4.7k\Omega$  pull resistor.

Additionally, each signal is equipped with an electronic protection array for ESD protection.

| Tuble of Digital 1/0 and 1/1 Real 1/0 Electrical Internace |                      |  |

|------------------------------------------------------------|----------------------|--|

| Protection                                                 | ±15kV ESD protection |  |

| Driver Level                                               | LVTTL (3.3V)         |  |

| Receiver                                                   | 5V tolerant          |  |

| Source current per line                                    | 15mA                 |  |

| Sink current per line                                      | 6mA                  |  |

Table 6. Digital I/O and P14 Rear I/O Electrical Interface

(Speedgoat, 2018)

#### 4.2 Signals Assignation/Identification

Once the available hardware components and its electrical performances were identified, next step was to identify the principal systems and groups of signals that BINMOV will be managing when testing the mechatronic devices.

The principal groups are control signals that will be transmitted from Speedgoat to the final actuator devices, data signals used to communicate sensors information, fast instrumentation signals used to detect abnormal behavior, and slow signals employed to identify each mechatronic assembly under test.

The assignation task was achieved by mapping all signals to the card modules pins, in this way we define the signals going from Speedgoat to the Bay and after conditioning and level conversion at this stage, the corresponding signals going from the Bay to final mechatronic device under test and vice versa.

For instance, an extrait of the signals identified going from Speedgoat to the Bay is showed in Table 7 where we can notice which final device the signal corresponds to, the number pin where it is connected to, the card module associated (IO35) and the type of signal (analog differential). This table is quite extensive comprising the 3 Speedgoat card modules, however an extrait is presented to give the lector a general idea of the signal routing.

| Carte             | Port                         | N° | Pin              | Dispositif      | Signal Name |

|-------------------|------------------------------|----|------------------|-----------------|-------------|

|                   |                              |    | 1                | •               | LVDT V1 +   |

|                   |                              | 1  | 51               |                 | LVDT V1 -   |

|                   |                              | 2  | 2                | DARC            | LVDT V2 +   |

|                   |                              |    | 52               | DARS            | LVDT V2 -   |

|                   |                              | 3  | 3                |                 | LVDT V +    |

|                   |                              | 3  | 53               |                 | LVDT V -    |

|                   |                              |    | 4                |                 | LVDT V1 +   |

|                   |                              | 4  | 54               |                 | LVDT V1 -   |

|                   |                              | 5  | 5                | BANC            | LVDT V2 +   |

|                   |                              | 5  | 55               | BANC            | LVDT V2 -   |

|                   |                              | 6  | 6                |                 | LVDT V +    |

|                   |                              | 6  | 56               |                 | LVDT V -    |

|                   |                              | 7  | 7                | COMBO Temp      | COM +       |

|                   |                              | '  | 57               | СОМ             | COM -       |

|                   |                              |    | 8                | COMBO Temp      | MON +       |

|                   |                              | 8  | 58               | MON             | MON -       |

| 2]                |                              |    | 9                | GND             |             |

| S.                | -                            |    | 59               | GND             |             |

| [200 kSPS]        | Analog Inputs (Differential) | 9  | 10               | COMBO Tension   | COM +       |

| 50                | ent                          | 9  | 60               | СОМ             | COM -       |

| <u> </u>          | ere                          | 10 | 11               | COMBO Tension   | MON +       |

| U                 | if                           | 10 | 61               | MON             | MON -       |

| ů l               | 0                            | 11 | 12               | COMBO Courant   | COM +       |

| na                | rts                          | 11 | 62               | СОМ             | COM -       |

| IO135-Performance | Idu                          | 12 | 13               | COMBO Courant   | MON +       |

| erf               |                              |    | 63               | MON             | MON -       |

| ă                 | Ő                            | 12 | 14               | Moniteur BUS    | + 24 VC +   |

| 35                | <b>N</b> a                   | 13 | 64 Moniteur BUS  | +24 VC -        |             |

| 0                 | 4                            | 14 | 15               | Monitour DUC    | + 24 VP +   |

| -                 |                              | 14 | 65               | 65 Moniteur BUS | + 24 VP -   |

|                   |                              | 15 | 16               | Moniteur BUS    | + 5 VC +    |

|                   |                              | 15 | 66               | WOTILEUL BUS    | + 5 VC -    |

|                   |                              |    | 17               | Monitour DUC    | - 5 VC +    |

|                   |                              |    | 67               | Moniteur BUS    | - 5 VC -    |

|                   |                              | 10 | 18               | GND             |             |

|                   |                              | 16 | 68               | GND             |             |

|                   |                              |    | 19               |                 | + 15 VP +   |

|                   |                              |    | 69               | Moniteur BUS    | + 15 VP -   |

|                   |                              | 47 | 20               | D SEMIKRON 1    | TEMP 1 (10) |

|                   |                              | 17 | 70               |                 |             |

|                   |                              | 10 | 19 21 SEMIKDON 2 | TEMP 2 (11)     |             |

|                   |                              | 18 | 71               | SEMIKRON 2      |             |

**Table 7.** Extrait of signals going from Speedgoat to the Bay.

Novatem Property: All rights Reserved / Reproduction, Disclosure and Exploitation Forbidden.

In the same way Table 8 shows un extrait of the pin assignation but this time regarding the signals that output from the Bay to the final mechatronic device like power signals, excitation, and monitoring signals.

|        |     | Connector | PIN | Signal Name                | Code name   | Signal type  |

|--------|-----|-----------|-----|----------------------------|-------------|--------------|

|        |     |           | A   | Motor phase 2              | ELM POW-Ph2 | Power supply |

|        | оυт | Power     | В   | Motor phase 1              | ELM POW-Ph1 | Power supply |

|        |     |           | D   | Motor phase 3              | ELM POW-Ph3 | Power supply |

|        |     |           | 2   | POB Power supply           | POB_POW-H   | Power supply |

|        |     |           | 3   | POB Power supply Return    | POB_POW-L   | Power supply |

|        | OUT |           | 5   | LVDT excitation            | VP+         | Power supply |

|        |     |           | 22  | LVDT excitation Return     | VP-         | Power supply |

| l .    |     |           | 7   | LVDT Output V1             | V1+         | Measurement  |

|        | IN  |           | 8   | LVDT Output V1 Return      | V1-         | Measurement  |

|        |     |           | 9   | LVDT Output V2             | V2+         | Measurement  |

| DADC   |     |           | 24  | LVDT Output V2 Return      | V2-         | Measurement  |

| DARS   |     | Signal    | 15  | PTS COM Power              | LV10_COM-H  | Power supply |

|        |     |           | 28  | PTS COM Power Return       | LV10_COM-L  | Power supply |

|        |     |           | 13  | PTS COS Output             | COS_COM-H   | Measurement  |

|        | IN  |           | 12  | PTS COS Output Return      | COS_COM-L   | Measurement  |

|        |     |           | 26  | PTS SIN Output Return      | SIN_COM-L   | Measurement  |

|        |     |           | 11  | PTS SIN Output             | SIN_COM-H   | Measurement  |

|        |     |           | 31  | PTS MON Power              | LV10_MON-H  | Power supply |

|        |     | -         | 37  | PTS MON Power return       | LV10_MON-L  | Power supply |

|        |     |           | 30  | PTS TEMP MON Output        | TEMP_MON-H  | Measurement  |

|        | IN  |           | 36  | PTS TEMP MON Output Return | TEMP_MON-L  | Measurement  |

|        |     |           | 33  | PTS TEMP COM Output        | TEMP_COM-H  | Measurement  |

|        |     |           | 34  | PTS TEMP COM Output Return | TEMP_COM-L  | Measurement  |

|        |     |           |     | 1                          |             |              |

| PARKER | OUT |           |     | 2                          |             |              |

|        |     |           |     | 3                          |             |              |

|        |     |           |     | LVDT V1 +                  |             |              |

|        | IN  |           |     | LVDT V1 -                  |             |              |

| BANC   |     |           |     | LVDT V2 +                  |             |              |

|        |     |           |     | LVDT V2 -                  |             |              |

|        | OUT |           |     | Excitation +               |             |              |

|        |     |           |     | Excitation -               |             |              |

**Table 8.** Extrait of signals going from the Bay to Speedgoat.

Novatem Property: All rights Reserved / Reproduction, Disclosure and Exploitation Forbidden.

#### 4.3 Selection of the communication protocol.

As the modules IO333-6 and IO333-2 support SPI and I2C communication respectively, it was a key decision to determine among these two communication protocols which one BINMOV will implement to communicate data, monitoring and control signals. Next sections show a brief description and main characteristic of each protocol.

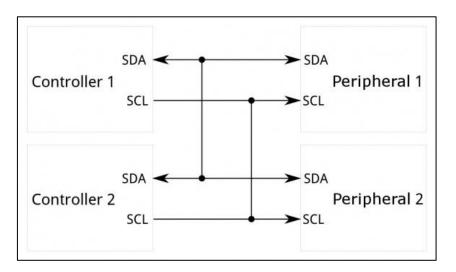

#### **Inter-Integrated Circuit Protocol - I2C**

The Inter-Integrated Circuit Protocol (I2C) is a serial communication protocol intended to allow the connection of multiple "speripheral devices" with one or more "controller devices" in a single bus to transmit data (Figure 8). It is only intended for short distance communications within a single device like the Serial Peripheral Interface (SPI) and only requires two signal wires to exchange information like Asynchronous Serial Interfaces such as RS-232 or UARTs (Sparkfun, 2013).

Figure 8. Inter-Integrated Circuit (I2C) Protocol. (Sparkfun, 2013)

SDA (Serial Data): The line for the master and slave to send and receive data.

I2C is a serial communication protocol so data is transferred bit by bit along this line.

SCL (Serial Clock): The line that carries the clock signal. I2C is synchronous, so the output of bits is synchronized to the sampling of bits by a clock signal. The clock signal is always controlled by the master.

| Table 9. I2C Main characteristics |                           |  |  |  |

|-----------------------------------|---------------------------|--|--|--|

| Wires Used                        | 2                         |  |  |  |

| Maximum Speed                     | Standard mode= 100 kbps   |  |  |  |

|                                   | Fast mode= 400 kbps       |  |  |  |

|                                   | High speed mode= 3.4 Mbps |  |  |  |

|                                   | Ultra fast mode= 5 Mbps   |  |  |  |

| Synchronous or Asynchronous?      | Synchronous               |  |  |  |

| Serial or Parallel?               | Serial                    |  |  |  |

| Max # of Masters                  | Unlimited                 |  |  |  |

| Max # of Slaves                   | 1008                      |  |  |  |

| (Campbell S                       | 5. , 2016)                |  |  |  |

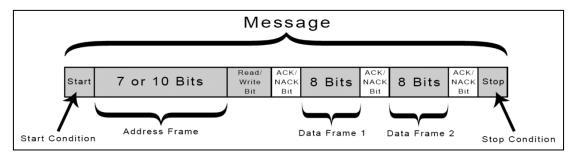

To transmit data, messages are broken up into frames of data (Figure 9). Each message contains the address frame that includes the binary address of the slave, and one or more data frames that contain the data being transmitted. The message also includes start and stop conditions, read/write bits, and ACK/NACK bits between each data frame.

Figure 9. I2C message frame (Campbell S., 2016)

- Start Condition: The SDA line switches from a high voltage level to a low voltage level before the SCL line switches from high to low.

- **Stop Condition:** The SDA line switches from a low voltage level to a high voltage level after the SCL line switches from low to high.

- Address Frame: A 7- or 10-bit sequence unique to each slave that identifies the slave the master wants to talk to.

- Read/Write Bit: A single bit specifying whether the master is sending data to the slave (low voltage level) or requesting data from it (high voltage level).

- ACK/NACK Bit: Each frame in a message is followed by an acknowledge/noacknowledge bit. If an address frame or data frame was successfully received, an ACK bit is returned to the sender from the receiving device (Campbell S., 2016).

#### Serial Peripheral Interface - SPI

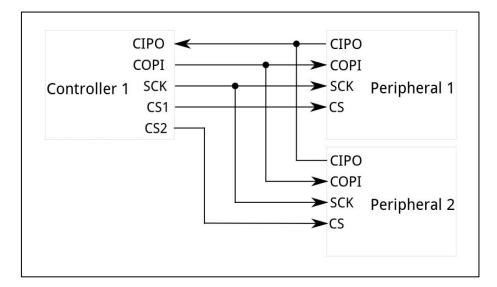

The Serial Peripheral Interface protocol requires at least 4 lines to connect a single controller to a single peripheral (Figure 10), each additional peripheral device requires one additional chip select I/O pin on the controller.

One benefit of SPI is that data can be transferred without interruption and any number of bits can be sent or received in a continuous stream, however SPI only allows one controller on the bus, but it does support an arbitrary number of peripherals (Campbell S. , 2013).

The increment of pins becomes the principal drawback in situations where lots of devices must be connected to one controller. Also, the large number of connections for each device can make routing signals more difficult in tight PCB layout designs (Sparkfun, 2013).

Figure 10. Serial Peripheral Interface (SPI) protocol. (Sparkfun, 2013)

- **MOSI (Master Output/Slave Input):** Line for the master to send data to the slave.

- MISO (Master Input/Slave Output): Line for the slave to send data to the master.

- SCLK (Clock): Line for the clock signal.

- SS/CS (Slave Select/Chip Select): Line for the master to select which slave to send data to.

| Wires Used                   | 4                                        |  |

|------------------------------|------------------------------------------|--|

| Maximum Speed                | Up to 10 Mbps                            |  |

| Synchronous or Asynchronous? | Synchronous                              |  |

| Serial or Parallel?          | Serial                                   |  |

| Max # of Masters 1           |                                          |  |

| Max # of Slaves              | Theoretically unlimited*                 |  |

| ((                           | $S_{\text{comphall}} = \frac{2}{2} (12)$ |  |

Table 10. SPI main characteristics.

To summarize, Table 11 shows a brief comparison between I2C and SPI. Considering the characteristics of each protocol, and the nature of BINMOV where several modules are going to be intercommunicated, where a significant but not too large amount of data must be sent and received between the modules and the controller

<sup>(</sup>Campbell S., 2013)

(Speedgoat) and also considering the restricted size of the Bay, the fact that the physical wiring should be as minimum as possible and the limited number of pins, I2C protocol was stablished as the main communication interface in BINMOV

| Table 11. | I2C vs | SPI |

|-----------|--------|-----|

|-----------|--------|-----|

|     | Advantages                                                                                                        | Drawbacks                                                                                                                       |

|-----|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| I2C | Only uses two wires                                                                                               | Slower data transfer rate than SPI                                                                                              |

|     | <ul> <li>Supports multiple masters and<br/>multiple slaves</li> </ul>                                             | • The size of the data frame is limited to 8 bits                                                                               |

|     | <ul> <li>ACK/NACK bit gives confirmation<br/>that each frame is transferred<br/>successfully</li> </ul>           | <ul> <li>More complicated hardware needed<br/>to implement than SPI</li> </ul>                                                  |

|     | <ul> <li>Hardware is less complicated than with UARTs</li> </ul>                                                  |                                                                                                                                 |

|     | • Well known and widely used protocol                                                                             |                                                                                                                                 |

| SPI | <ul> <li>No start and stop bits, so the data can<br/>be streamed continuously without<br/>interruption</li> </ul> | <ul> <li>Uses four wires (I2C and UARTs use two)</li> </ul>                                                                     |

|     | <ul> <li>No complicated slave addressing system like I2C</li> </ul>                                               | <ul> <li>No acknowledgement that the data has been successfully received</li> <li>No form of error checking like the</li> </ul> |

|     | <ul> <li>Higher data transfer rate than I2C<br/>(almost twice as fast)</li> </ul>                                 | <ul> <li>No form of enfor checking like the parity bit in UART</li> <li>Only allows for a single master</li> </ul>              |

|     | <ul> <li>Separate MISO and MOSI lines, so<br/>data can be sent and received at the<br/>same time</li> </ul>       | only anons for a single master                                                                                                  |

(Campbell S., 2016)

## 5. RESEARCH METHODOLOGY AND DESIGN

#### 5.1 Card Identification

BINMOV's electronic modules must sense data, condition them into the appropriate electronic levels and transmit them to Speedgoat, the Real-Time Target Machine. Therefore, one should know where data comes from, which module is transmitting to identify which kind of signals we are reading and which final mechatronic device under test we are looking at.

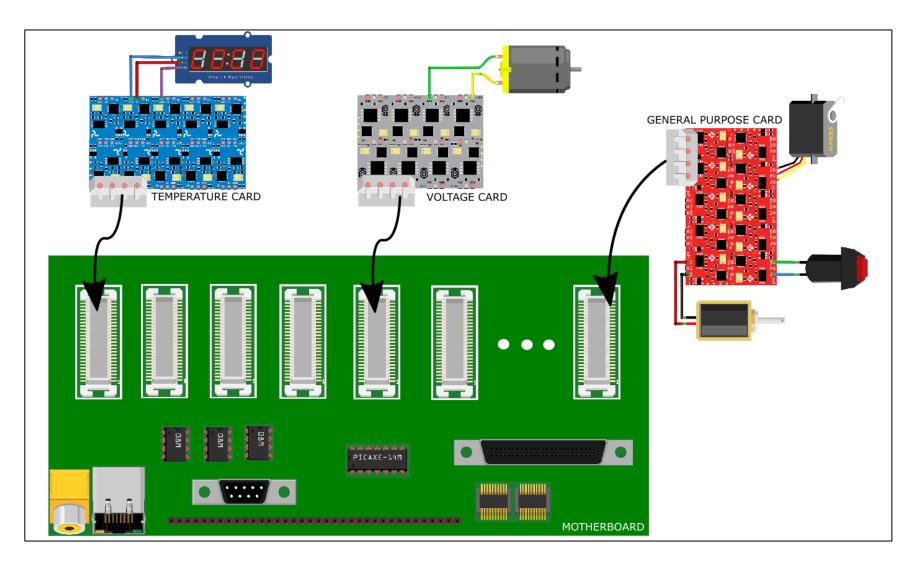

To achieve this signal identification, BINMOV envisages to develop a series of card modules built in a plug-in concept. Each one of these cards can be mounted in a motherboard, the idea is that each card contains a small circuit dedicated to provide a unique identifier for the card itself.

This identification will allow distinguish which card is plugged in the motherboard and like that one can know which signal is being transmitted. BINMOV being a project whose one of its purposes is the modularity and the capability of testing of a large number of developed and new devices, it envisages creating several card modules, for instance, the main cards for testing an engine will consist in a voltage, current, torque and temperature modules, each one will have its own identifier and in case if a similar engine smaller, more powerful or bigger should be tested in another project, a new group of cards according to the new voltage, current levels will be developed implying new identifiers but with the idea that it will be enough to plug-in the new cards into the motherboard and BINMOV will be ready to test the new device without additional electronics.

Figure 11 represents a general view how the motherboard will contain several interchangeable modules, each module dedicated to a specific control or measuring task,

with a single identifier that allows to recognize the type of card and the position where it is connected.

The key contribution to BINMOV project during the internship development was to conceptualize a solution that will deal with the identification task. Next sections describe the main stages and evolution of this conceptualization, going from analog solutions to digital ones, briefly presenting IC components according BINMOV requirements and finally designing, building, and testing a PCB prototype.

**Figure 11.** BINMOV's Motherboard and Card Modules representation Novatem Property: All rights Reserved / Reproduction, Disclosure and Exploitation Forbidde

#### 6. PROPOSED SOLUTIONS FOR CARD IDENTIFICATION

#### **6.1 Analog Solutions**

#### 6.1.1 Voltage Divider

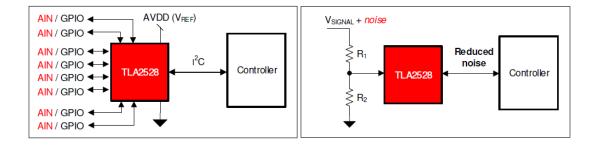

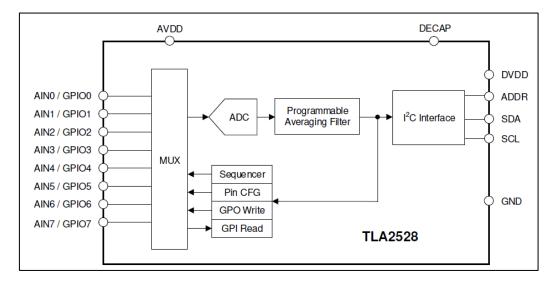

One proposed solution was to generate the identifiers with a single voltage divisor. The idea is to define different resistor values to generate as many tension levels as cards will be connected, then this voltage level will be read and converted to digital value thanks to an ADC, this ADC will send the digitalized voltage level through the I2C bus to Speedgoat.

Figure 12. TLA2528 Application (Texas Instruments, 2019)

Figure 12 represents the architecture that is being proposed, fortunately in the chips market there is enough performing devices dedicated to this kind of applications. The IC TLA2528 was selected to be implemented in this configuration because it integrates an internal multiplexer to read 8 different analog voltage levels, an ADC that can be connected directly to the bus because has an I2C interface.

Figure 13. TLA2528 Block Diagram (Texas Instruments, 2019)

The TLA2528 has an address selection pin that allows to choose 8 different addresses (Table 12), that means we can achieve to have until 64 card modules on the same bus.

| RESI               | STORS              | ADDRESS         |

|--------------------|--------------------|-----------------|

| R1 <sup>(1)</sup>  | R2 <sup>(1)</sup>  | ADDRESS         |

| 0 Ω                | DNP <sup>(2)</sup> | 001 0111b (17h) |

| 11 kΩ              | DNP <sup>(2)</sup> | 001 0110b (16h) |

| 33 kΩ              | DNP <sup>(2)</sup> | 001 0101b (15h) |

| 100 kΩ             | DNP <sup>(2)</sup> | 001 0100b (14h) |

| DNP <sup>(2)</sup> | DNP <sup>(2)</sup> | 001 0000b (10h) |

| DNP <sup>(2)</sup> | 11 kΩ              | 001 0001b (11h) |

| DNP <sup>(2)</sup> | 33 kΩ              | 001 0010b (12h) |

| DNP <sup>(2)</sup> | 100 kΩ             | 001 0011b (13h) |

Table 12. I2C Address selection

(Texas Instruments, 2019)

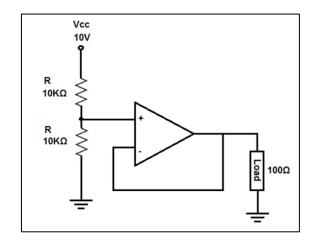

A closer look at the divisor suggests connecting an operational amplifier in the voltage output configured as common follower with an unitary gain (Figure 14). This additional component will help to guarantee the adequate voltage level when connecting the divisor to the IC.

Figure 14. Voltage Stabilizer Circuit using a Buffer

Therefore, an interactive excel sheet was developed to define the R2 values when R1 fixed to a defined value. Table 13 shows an extrait of the sheet for the first 10 tension values and the corresponding R2 values, these values can be adjusted according to the number of cards implemented, the input voltage and the desired power consumption in the divisor.

|    | <b>Binary Value</b> | Vc Voltage mV | Bit max diff | Voltage diff mV | R2 if R1 is |         | R2 diff | ZR       | I    | Р    |

|----|---------------------|---------------|--------------|-----------------|-------------|---------|---------|----------|------|------|

|    |                     |               | 100          | 80.57           | 10000       |         |         | Ohm      | mA   | mW   |

|    | 0                   | 0             |              |                 |             |         |         |          |      |      |

|    |                     |               | 50           | 40.28           |             | 123.58  |         |          |      |      |

| 1  | 100                 | 80.57         |              |                 | 250.25      |         | 256.55  | 10250.25 | 0.32 | 1.06 |

|    |                     |               | 150          | 120.85          |             | 380.13  |         |          |      |      |

|    |                     |               | 219          | 176.44          |             | 564.87  |         |          |      |      |

| 2  | 269                 | 216.72        |              |                 | 702.90      |         | 279.72  | 10702.90 | 0.31 | 1.02 |

|    |                     |               | 319          | 257.01          |             | 844.59  |         |          |      |      |

|    |                     |               | 388          | 312.60          |             | 1046.39 |         |          |      |      |

| 3  | 438                 | 352.88        |              |                 | 1197.38     |         | 306.16  | 11197.38 | 0.29 | 0.97 |

|    |                     |               | 488          | 393.16          |             | 1352.55 |         |          |      |      |

|    |                     |               | 557          | 448.75          |             | 1573.89 |         |          |      |      |

| 4  | 607                 | 489.04        |              |                 | 1739.75     |         | 336.55  | 11739.75 | 0.28 | 0.93 |

|    |                     |               | 657          | 529.32          |             | 1910.44 |         |          |      |      |

|    |                     |               | 726          | 584.91          |             | 2154.30 |         |          |      |      |

| 5  | 776                 | 625.20        |              |                 | 2337.35     |         | 371.69  | 12337.35 | 0.27 | 0.88 |

|    |                     |               | 826          | 665.48          |             | 2525.99 |         |          |      |      |

|    |                     |               | 895          | 721.07          |             | 2796.00 |         |          |      |      |

| 6  | 945                 | 761.35        |              |                 | 2999.05     |         | 412.64  | 12999.05 | 0.25 | 0.84 |

|    |                     |               | 995          | 801.64          |             | 3208.64 |         |          |      |      |

|    |                     |               | 1064         | 857.23          |             | 3509.23 |         |          |      |      |

| 7  | 1114                | 897.51        |              |                 | 3735.75     |         | 460.75  | 13735.75 | 0.24 | 0.79 |

|    |                     |               | 1164         | 937.79          |             | 3969.99 |         |          |      |      |

|    |                     |               | 1233         | 993.38          |             | 4306.67 |         |          |      |      |

| 8  | 1283                | 1033.67       |              |                 | 4560.97     |         | 517.79  | 14560.97 | 0.23 | 0.75 |

|    |                     |               | 1333         | 1073.95         |             | 4824.47 |         |          |      |      |

|    |                     |               | 1402         | 1129.54         |             | 5204.16 |         |          |      |      |

| 9  | 1452                | 1169.82       |              |                 | 5491.68     |         | 586.13  | 15491.68 | 0.21 | 0.70 |

|    |                     |               | 1502         | 1210.11         |             | 5790.29 |         |          |      |      |

|    |                     |               | 1571         | 1265.70         |             | 6221.78 |         |          |      |      |

| 10 | 1621                | 1305.98       |              |                 | 6549.49     |         | 668.94  | 16549.49 | 0.20 | 0.66 |

|    |                     |               | 1671         | 1346.26         |             | 6890.72 |         |          |      |      |

Table 13. R2 values when R1 is fixed

Novatem Property: All rights Reserved / Reproduction, Disclosure and Exploitation Forbidden.

#### 6.1.2 Voltage reference

As there will be at least 64 different card modules, to achieve a correct identification, resistors must guarantee the appropriate voltage levels, that means that the input tension should be very stable all the time and the resistor selected high-performing so there will be no fluctuation at the output.

For instance, if we set an input voltage like Vin = 3.3 [V] and considering the TLA2528 ADC resolution N = 12, the less significant bit is LSB = 0.8057 [mV]. So, we should mange tension in the millivolts range by simply changing the resistors, evidently the resistor value should be as close as possible to the determined in the green column, however in the market there is standard resistor values and sometimes the available component does not match the required value.

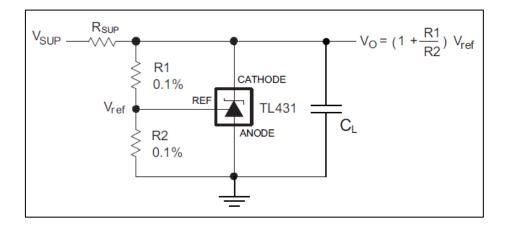

To face this constraint, the solution proposed is to use a voltage reference. The main benefit of using this component is that the output voltage will remain stable so that we can guarantee a different tension level for each module, the division is also done by using two resistors, but as we have large input and output voltage (up to V = 36 [V] for TL431) there is less risk to overlap the output tension level when choosing the commercial resistor values.

Figure 15. Shunt Regulator Schematic (Texas Instruments, 2014)

To program the cathode voltage to a regulated voltage a resistive bridge must be shunted between the cathode and anode pins with the midpoint tied to the reference pin. This can be seen in Figure 15, with R1 & R2 being the resistive bridge. The cathode/output voltage in the shunt regulator configuration can be approximated by the equation (Texas Instruments, 2014).

$$V_o = (1 + \frac{R_1}{R_2})V_{ref}$$

The proposed solutions could have worked if they had been implemented, however at this stage, NOVATEM BINMOV's committee decided to take the digital way because from their experience the environment where this circuit is going to be implement has electromagnetic compatibility issues, the signal quality is going to be degraded, some data will be lost when performing the ADC, the transmission, and the DAC. Therefore, a new solution was required but this time using high or low levels, the new approach to face the identification task is explained in next section.

#### **6.2 Digital Solutions**

To identify different cards, the proposed digital solution envisages the use of an integrated circuit which allows the communication of data via the I2C protocol, so that we can send the unique identifier associated with each type of card trough this bus.

I2C communication is done through a unique address, specific to each device on the bus, it is this identifier that allows the devices to recognize who is sending the message and who will receive it. However, since ICs are used, it is the manufacturers in general who have already set the address linked to each of the devices.

In this context, we are limited by the number of devices (same kind of devices) that we can put in the communication bus. There are some ICs that have dedicated addressing pins, then it is possible to configure in the device another address so that we can have multiple components on the same bus. However, the same manufacturer limits the addressing by the number of pins dedicated to this function, in the best case it is possible to have 8 different addresses which means that we are limited to connecting 8 ICs on the bus if we use the same chip.

In order to overcome this limitation, it is proposed to use an IC capable of managing the identification of several cards. If we use a byte for the card's identifier, we will have the possibility of having up to 255 different types of cards knowing that we reserve the identifier 0000 0000 when there is no module on the motherboard. So, three new solutions were proposed.

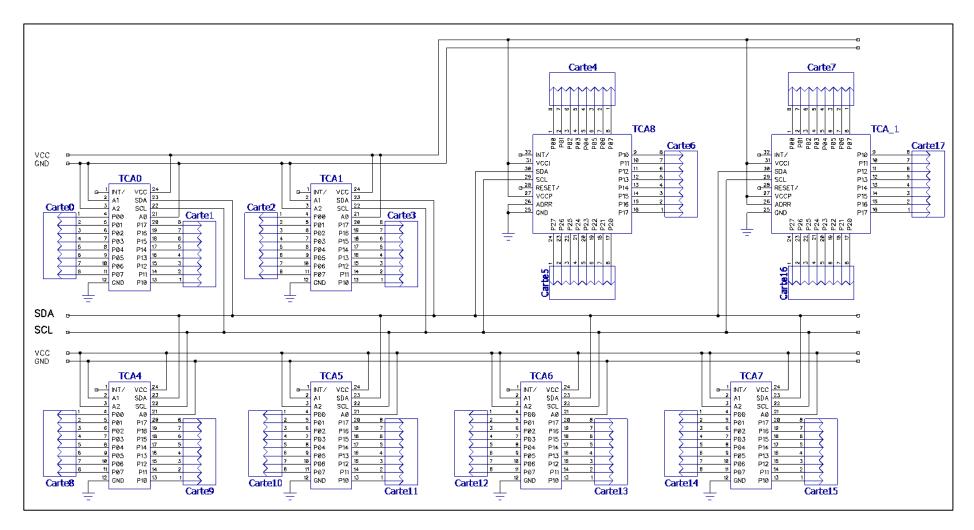

# 6.2.1 Solution 1: 8 TCA9555 Chip Implementation – Until 16 modules on the motherboard

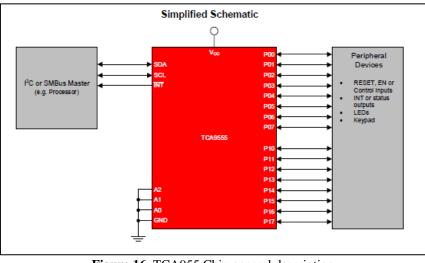

An assemble of 8 chips TCA9555 on the same bus will allow to have until 16 different cards because this IC owns 3 configurable slave address pins and 2 ports of 8 bits each (Figure 16), so each one of them can manage a pair of devices at the same time. The chip main characteristics are stated:

- 400-kHz Fast I2C Bus

- Configurable Slave Address with 3 Address Pins

- Low Standby-Current Consumption of 3.5 μA Maximum

- 16-bit I2C to Parallel Port Expander

- General-purpose remote I/O expansion for most microcontroller families via the I2C

- Designed for 1.65-V to 5.5-V VCC operation

- At power on, the I/Os are configured as inputs. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits (Texas Instruments, 2019).

Figure 16. TCA955 Chip general description (Texas Instruments, 2019)

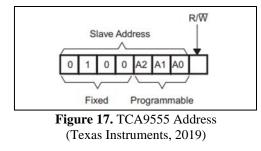

As stated, the slave address selection is done by connecting the pins A2, A1 and A0 to +Vcc or GND (Figure 17). The last bit corresponds to the type of operation that we perform on the device, 1 if we read the ports' state, or 0 if we want to write on these ports.

This selection address pins allow to have according to the manufacturer a maximum of 8 different devices on the same I2C bus as depicted in the Table 14.

| I <sup>2</sup> C BUS SLAVE ADDRESS |  |  |  |  |  |  |  |  |  |

|------------------------------------|--|--|--|--|--|--|--|--|--|

| SEAVE ADDRESS                      |  |  |  |  |  |  |  |  |  |

| I), 0x20 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

| I), 0x21 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

| I), 0x22 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

| I), 0x23 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

| I), 0x24 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

| I), 0x25 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

| I), 0x26 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

| I), 0x27 (hexadecimal)             |  |  |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |  |  |

(Texas Instruments, 2019)

A typical application of this component proposed by the fabricant is detailed in the following diagram (Figure 18) where the TCA9555 is used to control subsystems which are generally far from the master (processor - microcontroller). The TCA955 is dedicated to manage discrete signals 1 or 0 generally related to enabling, reset, activation, inactivation of other devices and it can also read other devices' outputs and send this data to the master through the I2C bus.

(Texas Instruments, 2019)

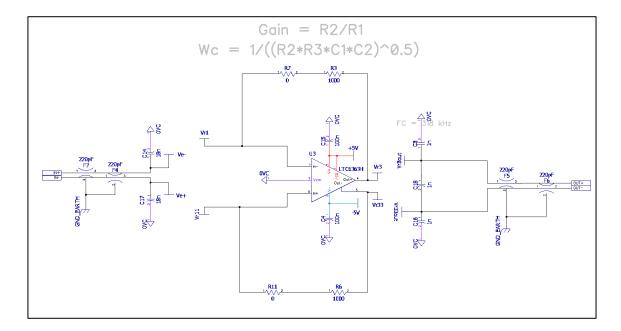

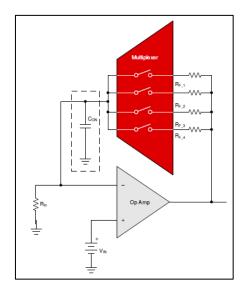

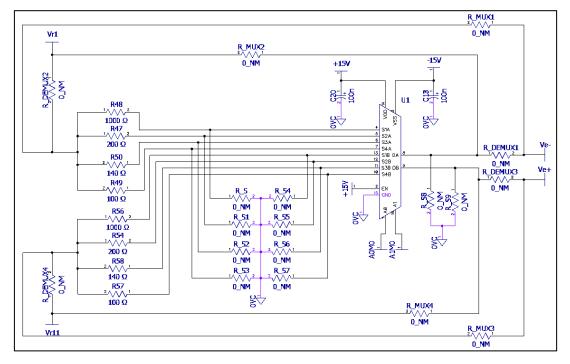

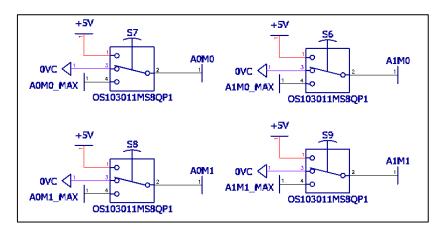

## **Fault Detection**