### UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ

**Colegio de Posgrados**

# Design of CMOS physical unclonable functions for hardware security application

## Tesis en torno a una hipótesis o problema de investigación y su contrastación

### Kevin Andrés Vicuña Barriga

### Felice Crupi, Ph.D. Director de Trabajo de Titulación

Trabajo de titulación de posgrado presentado como requisito para la obtención del título de Master en Nanoelectrónica

Quito, 16 de diciembre del 2022

## UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ COLEGIO DE POSGRADOS

### HOJA DE APROBACIÓN DE TRABAJO DE TITULACIÓN

Design of CMOS physical unclonable functions for hardware security application

### Kevin Vicuña

Colegio de Ciencias e Ingenierías

| Nombre del Director del Programa:        | Luis Miguel Prócel          |

|------------------------------------------|-----------------------------|

| Título académico:                        | Doctor of Philosophy        |

| Director del programa de:                | Maestría en Nanoelectrónica |

|                                          |                             |

|                                          |                             |

| Nombre del Decano del colegio Académico: | Eduardo Alba                |

| Título académico:                        | Doctor of Philosophy        |

Nombre del Decano del Colegio de Posgrados:Hugo BurgosTítulo académico:Doctor of Philosophy

Decano del Colegio:

Quito, Diciembre 2022

### © DERECHOS DE AUTOR

Por medio del presente documento certifico que he leído todas las Políticas y Manuales de la Universidad San Francisco de Quito USFQ, incluyendo la Política de Propiedad Intelectual USFQ, y estoy de acuerdo con su contenido, por lo que los derechos de propiedad intelectual del presente trabajo quedan sujetos a lo dispuesto en esas Políticas.

Asimismo, autorizo a la USFQ para que realice la digitalización y publicación de este trabajo en el repositorio virtual, de conformidad a lo dispuesto en la Ley Orgánica de Educación Superior del Ecuador.

Nombre del estudiante:

Código de estudiante:

00322858

Kevin Vicuña

C.I.:

1718186214

Lugar y fecha:

Quito, 16 de diciembre de 2022

### ACLARACIÓN PARA PUBLICACIÓN

**Nota:** El presente trabajo, en su totalidad o cualquiera de sus partes, no debe ser considerado como una publicación, incluso a pesar de estar disponible sin restricciones a través de un repositorio institucional. Esta declaración se alinea con las prácticas y recomendaciones presentadas por el Committee on Publication Ethics COPE descritas por Barbour et al. (2017) Discussion document on best practice for issues around theses publishing, disponible en http://bit.ly/COPETheses.

### **UNPUBLISHED DOCUMENT**

**Note:** The following graduation project is available through Universidad San Francisco de Quito USFQ institutional repository. Nonetheless, this project – in whole or in part – should not be considered a publication. This statement follows the recommendations presented by the Committee on Publication Ethics COPE described by Barbour et al. (2017) Discussion document on best practice for issues around theses publishing available on http://bit.ly/COPETheses.

### DEDICATORIA

Dedicato a tutte le persone che mi hanno affiancato e sostenuto in questi due anni di studio.

### AGRADECIMIENTOS

Ringrazio i miei docenti, Felice Crupi, Lionel Trojman, Luis Miguel Procel e Ramiro Taco.

Ringrazio Massimo Vatalaro per avermi seguito nella scrittura del mio elaborato finale.

Ringrazio i miei nonni, Laura Olivo, Gerardo Barriga e Glady Palau.

Ringrazio Katherine Rossella Foglia per essermi stata vicina e avermi motivato e aiutato nello svolgimento di questo elaborato.

Ringrazio mio padre, mia madre e mia sorella per essere sempre stati presenti nel momento del bisogno e avermi motivato a raggiungere questo obiettivo.

#### **RESUMEN**

Esta tesis presenta el desarrollo de diferentes funciones físicamente no clonables (PUFs) CMOS para aplicaciones de seguridad hardware. Basándose en la forma en que las variaciones del proceso se traducen en una respuesta binaria, las PUFs pueden clasificarse en diferentes clases. En este proyecto nos centraremos en las estructuras estáticas y dinámicas.

El circuito estático analizado se basa en un divisor de tensión metaestable de cuatro transistores que trabajan en el régimen subumbral junto con un inversor en la etapa de salida. El circuito dinámico que se implementó está basado en un oscilador en anillo, el diseño de este circuito utiliza una topología de celda de retardo que incorpora un transistor de paso tipo PMOS entre dos etapas sucesivas con el objetivo de modificar la variabilidad del tiempo de respuesta de la celda. Se realizó una comparación de las distintas soluciones con el virtuoso TCAD y la tecnología TSMC de 180nm. Analizamos los resultados de los PUF en términos de estabilidad, reproducibilidad, unicidad y consumo de energía.

Palabras clave: Diseño CMOS, seguridad de hardware, Internet de las cosas (IoT), función físicamente no clonable (PUF), divisor de tensión, oscilador en anillo, comparador de base de colapso.

#### ABSTRACT

This thesis presents the development of different CMOS physically unclonable functions (PUFs) for hardware security application. Based on the way in which process variations are translated into a binary response PUFs can be categorized in different class. In this project we will focus on static and dynamic structures.

The static circuit that was analyzed is based on a metastable voltage divider of four transistors working in the subthreshold regime together with an inverter in the output stage. The dynamic circuit that was implemented is based on a ring oscillator, the design of this circuit uses a delay cell topology that incorporates a PMOS type pass transistor between two successive stages with the aim of modifying the variability of the cell response time. A comparison of the different solutions with the virtuoso TCAD and the 180nm TSMC technology was carried out. We analyze the results of the PUFs in terms of stability, reproducibility, uniqueness and power consumption.

**Key words:** CMOS design, hardware security, Internet of Things (IoT), physically unclonable function (PUF), voltage divider, ring oscillator, collapse base comparator.

### TABLA DE CONTENIDO

| Dedicatoria                                             | 5  |

|---------------------------------------------------------|----|

| Agradecimientos                                         | 6  |

| Resumen                                                 | 7  |

| Abstract                                                | 8  |

| Tabla de contenido                                      | 9  |

| índice de TABLAS                                        | 11 |

| ÍNDICE DE FIGURAS                                       | 12 |

| Introduction                                            | 15 |

| Physical Disorder in Integrated Circuits                |    |

| Devices Geometry                                        |    |

| Devices Material                                        |    |

| Interconnects Geometry                                  |    |

| Interconnects Material                                  |    |

| Design of a Physically Unclonable Function              |    |

| Delay Based PUFs                                        |    |

| Arbiter                                                 |    |

| Ring Oscillator PUF                                     |    |

| Self-timed Rings PUF                                    |    |

| Current-Based PUFs                                      |    |

| Current-Based PUFs Using Transistors Arrays             |    |

| Current-Based PUFs Using Dynamic Random Access Memories |    |

| Voltage-Based PUFs                                      |    |

| SRAM PUFs                                               |    |

| Latch-Based PUFs                                        |    |

| Metrics of PUF Devices                                  |    |

| Uniqueness                                              |    |

| Reliability                                             |    |

| Uniformity                                              |    |

| Tamper Resistance                                       |    |

| •                                                       |    |

| Development and simulation methodology                  |    |

| Full custom metodology                                  |    |

| Technology                                              |    |

| Development software                                    |    |

| Proposed schemes and results                            |    |

| Metastable PUF bitcell                                  |    |

| Simulation Results of the PUF Bitcell                   |    |

| Delay Base PUF                                          |    |

| Inverter                                                |    |

| Ring Oscillator                                         |    |

| Calibrated Ring Oscillator                              |    |

| Calibrated ring oscillator collapse-based comparator    |    |

|                                                         |    |

| Conclusions |  |

|-------------|--|

| References  |  |

### ÍNDICE DE TABLAS

| 6 |

|---|

| 8 |

| 1 |

| 2 |

| 7 |

| 8 |

|   |

### ÍNDICE DE FIGURAS

| Figure 1.1: Devices Geometry Variation                                                      | 17 |

|---------------------------------------------------------------------------------------------|----|

| Figure 1.2: Devices Material Variation                                                      |    |

| Figure 1.3: Interconnects Geometry Variation                                                | 19 |

| Figure 1.4: Interconnects Material Variation                                                | 20 |

| Figure 1.5: The impact of variability on the electrical parameters of VLSI cir              |    |

| Figure 1.6: Conceptual Ring Oscillator PUF device.                                          |    |

| Figure 1.7: Fingerprinting as a physical method of cryptography                             | 24 |

| Figure 1.8: Architecture for silicon-based PUFs.                                            | 25 |

| Figure 1.9: PUF novel solution for cryptography                                             |    |

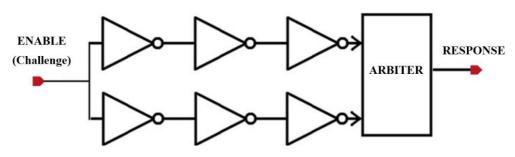

| Figure 1.10: A single challenge arbiter PUF.                                                | 27 |

| Figure 1.11: Circuit diagram of an arbiter based on an S-R latch                            |    |

| Figure 1.12: Structure of a multiple bit challenge arbiter PUF                              |    |

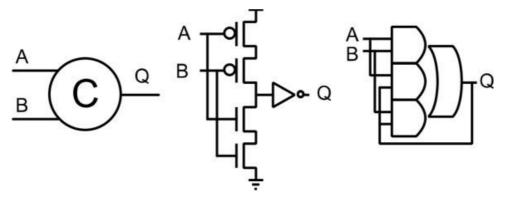

| Figure 1.14: Muller-C element                                                               |    |

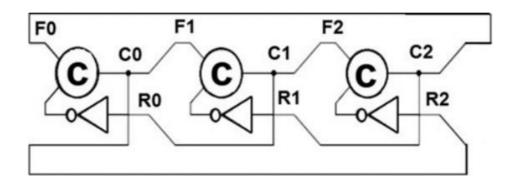

| Figure 1.15: Three stage self-timed ring (STR)                                              | 34 |

| Figure 1.16: Token and bubble movement.                                                     | 34 |

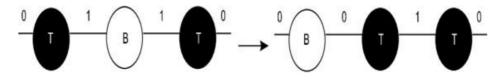

| Figure 1.17: Smart PUF based on self-timed ring structure                                   | 35 |

| Figure 1.18: A current-based PUF                                                            |    |

| Figure 1.19: Circuit schematic of the TCO unit array                                        |    |

| Figure 1.20: DRAM                                                                           | 41 |

| Figure 1.21: 6T-SRAM Schematic                                                              | 43 |

| Figure 1.22: Characteristics for SRAM                                                       | 44 |

| Figure 1.23: SRAM Memory Array                                                              | 45 |

| Figure 1.24: SR Latch                                                                       | 46 |

| Figure 1.25: Uniqueness evaluation of a PUF                                                 |    |

| Figure 1.26: Reliability evaluation of a PUF                                                | 49 |

| Figure 1.27: Uniformity response of a PUF                                                   | 49 |

| Figure 2.1: Evolution of the number of transistors every two years according<br>Moore's Law |    |

| Figure 2.2: Flow of custom design.                                                          |    |

| Figure 3.1: Conceptual diagram of the proposed PUF bitcell                                  |    |

| Figure 3.2: Metastability characteristic                                                                                                                           | .57  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.3: Transistor-Level scheme of the 4T bitcell                                                                                                              | . 58 |

| Figure 3.4: PUF bitcell with 2T-core                                                                                                                               | . 62 |

| Figure 3.5: PUF bitcell with 4T-core sizing                                                                                                                        | . 69 |

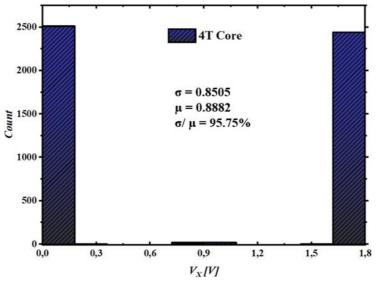

| Figure 3.6: Statistical distribution of the voltage $V_X$ of the bitcell core                                                                                      | .70  |

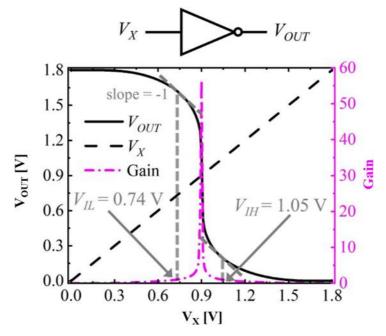

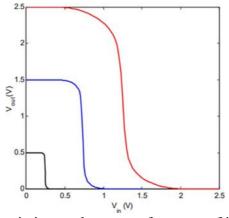

| Figure 3.7: Nominal input-output characteristics of the inverter                                                                                                   | .71  |

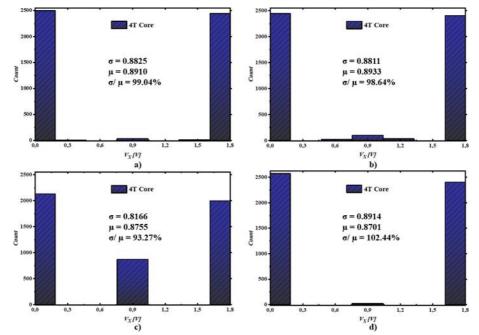

| Figure 3.8: Statistical distribution of the voltage VX of the bitcell core a) FF ,                                                                                 | .72  |

| b) SS, c) FS, d) SF corners                                                                                                                                        | .72  |

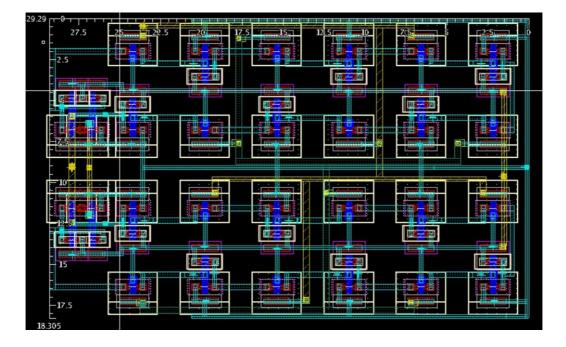

| Figure 3.9: PUF bitcell with 4T-core layout                                                                                                                        | .73  |

| Figure 3.10: Ring Oscillator bitcell                                                                                                                               | 74   |

| Figure 3.11: Voltage transfer curve of inverter V <sub>DD</sub> = 2.5[V ]                                                                                          | .76  |

| Figure 3.12: Device variations voltage transfer curve of inverter $V_{DD} = 2.5[V]$                                                                                | .78  |

| Figure 3.13: Voltage variations voltage transfer curve of inverter $V_{DD}$ = 2.5[V]                                                                               | .78  |

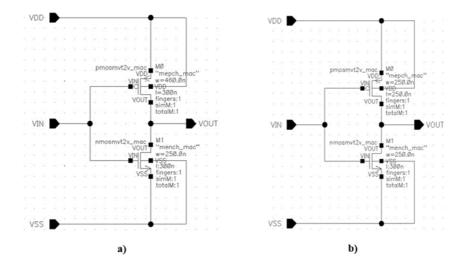

| Figure 3.14: Inverter gate schematic: a) transistor size V <sub>M</sub> = V <sub>DD</sub> , b) minimum                                                             | . 79 |

| transistor size NMOS and PMOS                                                                                                                                      | . 79 |

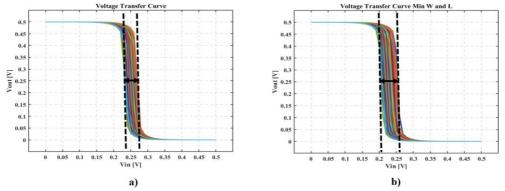

| Figure 3.15: Inverter VTC: a) transistor size VM = VDD , b) minimum transistor .                                                                                   | . 80 |

| size NMOS and PMOS                                                                                                                                                 | . 80 |

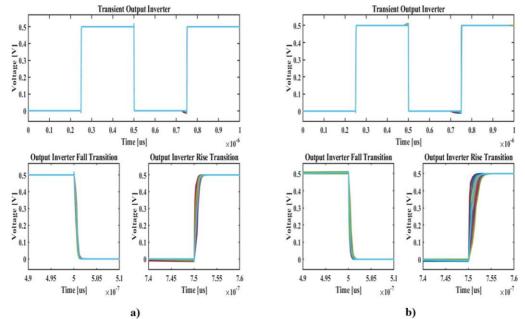

| Figure 3.16: Inverter transient response: a) transistor size VM = VDD , b)<br>minimum transistor size NMOS and PMOS                                                | . 80 |

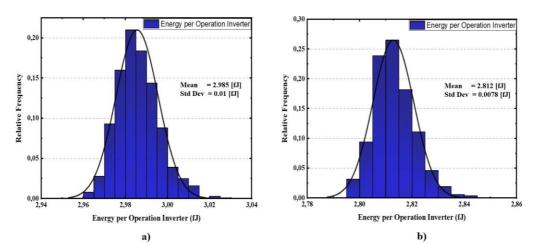

| Figure 3.17: Inverter energy per operation: a) transistor size VM = VDD , b)<br>minimum transistor size NMOS and PMOS                                              | 81   |

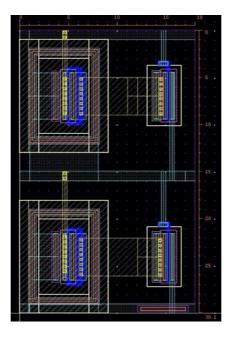

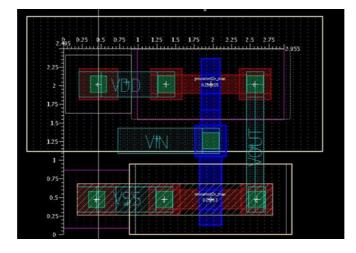

| Figure 3.18: Layout inverter minimum transistor size                                                                                                               | . 82 |

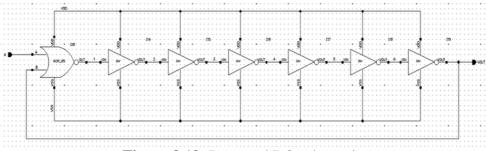

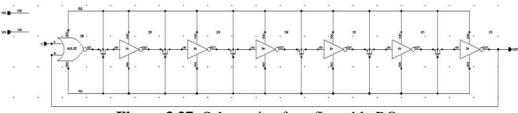

| Figure 3.19: Proposed RO schematic                                                                                                                                 |      |

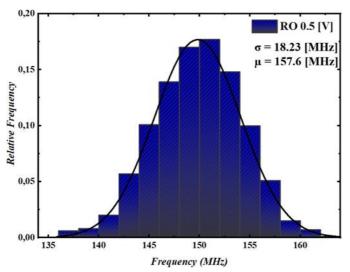

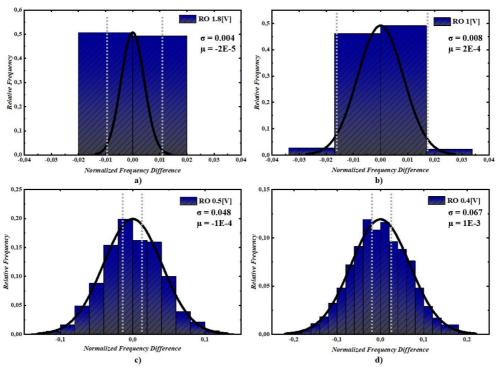

| Figure 3.20: Simulated distributions of the frequency of proposed RO-base                                                                                          | . 83 |

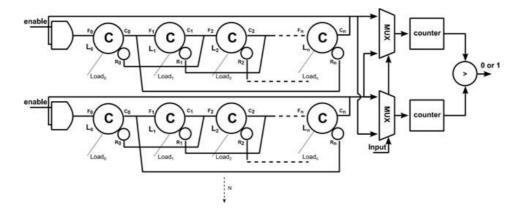

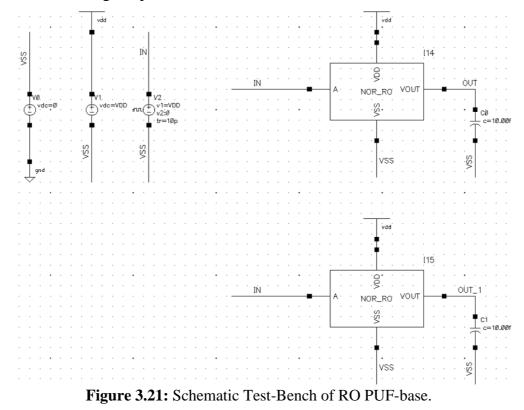

| Figure 3.21: Schematic Test-Bench of RO PUF-base                                                                                                                   | . 84 |

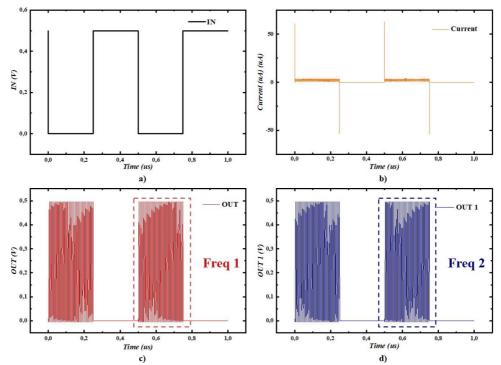

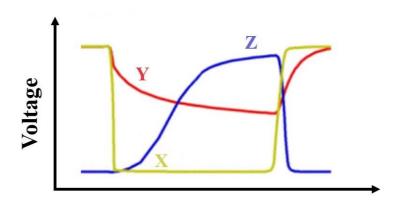

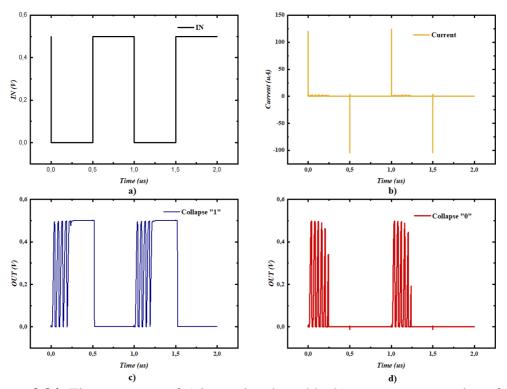

| Figure 3.22: Time response of a) input signal, enables oscillating circuits, b)<br>current consumption of the oscillators, c) response of the first oscillator and | 85   |

| d) response of the second oscillator                                                                                                                               | . 85 |

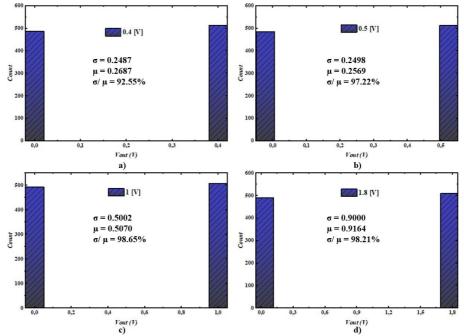

| Figure 3.23: Normalized frequency difference with different bias voltages a)<br>1.8[V], b) [V], c)0.5[V] and d)0.4[V]                                              | 86   |

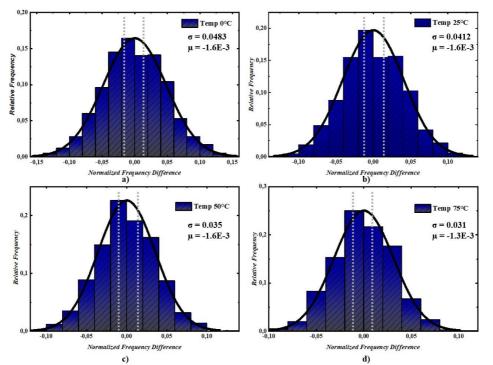

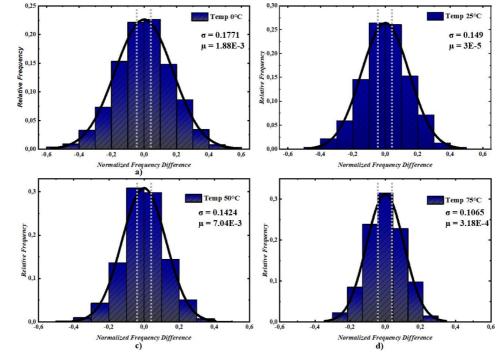

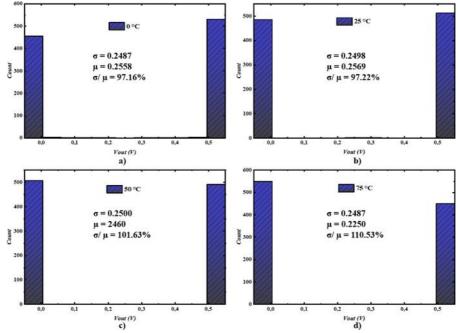

| Figure 3.24: Normalized frequency difference with bias voltage of 0.5[V] at<br>different temperatures a) 0ºC, b) 25ºC, c) 50ºC and d) 75ºC                         | 87   |

| Figure 3.25: Layout ring oscillator                                                                                                                                | . 88 |

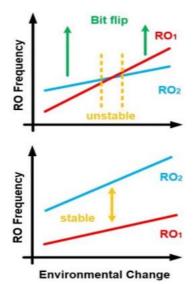

| Figure 3.26: Stability enhancement of an RO-based PUF                                                                                                              | . 89 |

| Figure 3.27: Schematic of configurable RO90                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.28: Effect of the PMOS pass transistor between two inverters                                                                                                                                                                                                  |

| Figure 3.29: Normalized frequency difference with respect to the nominal<br>frequency with different bias voltages a) 1.8[V], b) 1[V], c) 0.5[V] and d) 0.4[V]91                                                                                                       |

| Figure 3.30: Normalized frequency difference with respect to the nominal<br>frequency with bias voltage of 0.5[V] at different temperatures a) 0ºC, b) 25ºC, c)<br>50ºC and d)75ºC92                                                                                   |

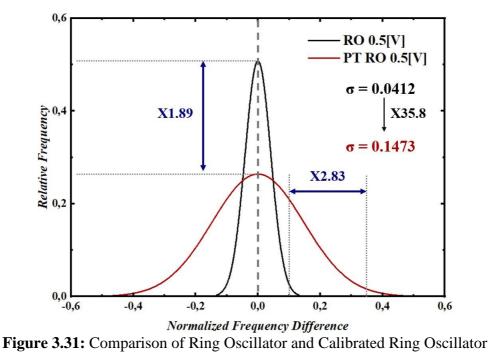

| Figure 3.31: Comparison of Ring Oscillator and Calibrated Ring Oscillator<br>Distributions                                                                                                                                                                             |

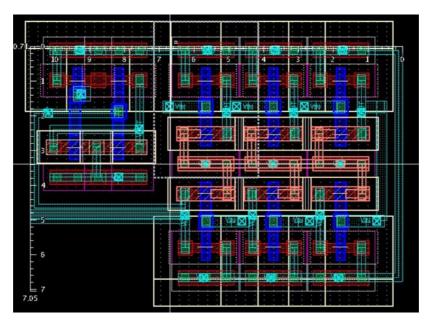

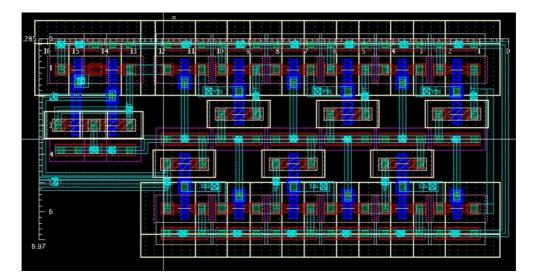

| Figure 3.32: Layout calibrated ring oscillator94                                                                                                                                                                                                                       |

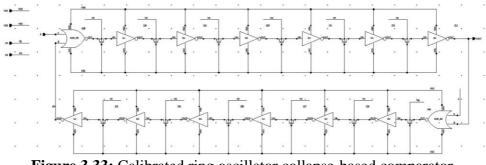

| Figure 3.33: Calibrated ring oscillator collapse-based comparator                                                                                                                                                                                                      |

| Figure 3.34: Time response of a) input signal, enable, b) current consumption of the PUF, c) response in the case that collapses OUT to $V_{DD}$ and d) response in the case that collapses OUT to $V_{DD}$ and d) response in the case that collapses OUT to $V_{SS}$ |

| Figure 3.35: PUF response with different bias voltages a) 1.8[V], b) 1[V], c) 0.5[V]<br>and d) 0.4[V ]                                                                                                                                                                 |

| Figure 3.36: PUF response with bias voltage of 0.5[V] at different temperatures .98                                                                                                                                                                                    |

| a) 0ºC, b) 25ºC, c) 50ºC and d) 75ºC98                                                                                                                                                                                                                                 |

| Figure 3.37: Layout of the proposed PUF cell99                                                                                                                                                                                                                         |

#### **INTRODUCTION**

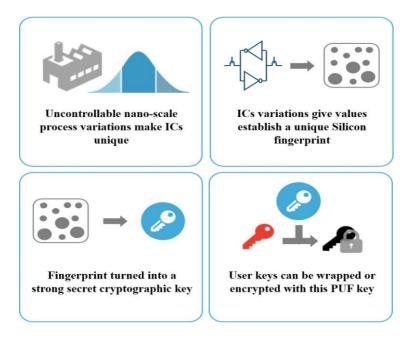

Nowadays, the development of the IoT scenario pushes the demand of preserving information down to the chip level. The security services (i.e., confidentiality, integrity, authentication, nonrepudiation and digital signature) required for preserving data are guaranteed by using a secret key (often called root of trust). However, the problem is the leakage of the key for which malicious users can perform actions that violate some basic requirements of the data transaction (such as data eavesdropping or password breaking) conventionally, the secret key is generated off-chip and stored in a nonvolatile memory (NVM) but this approach requires additional costs and suffers of reverse engineering attacks that may cause the leakage of the key. Ideally, the secret key should be generated in a volatile way when required without storing it in a NVM.

Physically unclonable functions (PUFs) are promising cryptographic primitives which exploits random static phenomena for generating unique, reproducible and random key in a volatile way. A PUF can be seen as a physical device, whose system could be considered simple, taking into account that it has a number of features that are very interesting for security applications. This is because this type of hardware should be able to have a simple evaluation, however, it should be impossible to predict. Another important aspect is that these devices should have relatively easy fabrication, nevertheless, their duplication should be difficult to achieve. The term PUF was first described in (Daihyun Lim and Lee, 2005), in this paper the authors also introduce a new expression "silicon PUF". Referring to all physically non-countable devices that are built and designed on integrated circuits (ICs). What makes silicon PUFs interesting is that they use the variations in the fabrication process that always exist between ICs to generate completely random responses.

It is important to note that PUFs could be fabricated from any other format than silicon. Some examples of PUF designs using other methods of randomizing results can be found in the literature. The most common would be optical devices, which exploit light scattering (Fournel, 2016), (Dolev, 2015). We can also find radio frequency (RF) designs, which use electromagnetic waves that are emitted from a device while it is operating (Reising, 2015), (Cobb, 2012). Like these examples there are several forms of identification schemes, however, for this project we will focus on silicon PUFs.

#### Physical Disorder in Integrated Circuits

When talking about integrated circuits we could say that they are synthetic; therefore it should be possible to design all their irregularities both in shape and structure. However, this is not the case in most modern chips, the main reason being variability. When we talk about variability in IC design, we refer to inaccuracies in the manufacturing processes. It also refers to temperature and voltage variations within the chip, causing a change in the performance and power consumption of the circuits (Nassif, 2007). This increases with the scaling of very large scale integrated circuit (VLSI) technologies, despite the improvement this has on performance and power consumption. Two sources of variation can be identified in systems implemented in real life (Narasimhan, 2007), (Nassif S. , 2001). The first factor is environmental, where changes in power, supply voltage, operating temperature and electrical degradation parameters in the devices occur. The second factor is the physical one, where variations in dimensions and structures are observed when manufacturing these devices.

#### **Devices Geometry**

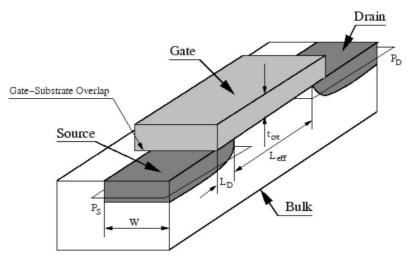

The variation of device geometry has some very clear examples, the one we will give the most importance and explain is the MOSFET structure in integrated circuits. This device usually includes the variation of thickness and lateral dimensions.

- Thickness variation occurs in gate oxide width (T(ox)), is a fundamental part and a parameter that is relatively easy to control. This type of effect is usually most evident when changing wafers.

- When talking about the lateral dimension, the channel width and length are taken into account, typically their variations are due to the photolithography process.

MOSFETs, especially in scaled devices, tend to be particularly sensitive to the effective channel length (Leff), this type of variation has to be considered as it directly impacts the current characteristic observed at the output (Chandrakasan, 2001).

Figure 1.1: Devices Geometry Variation.

#### **Devices Material**

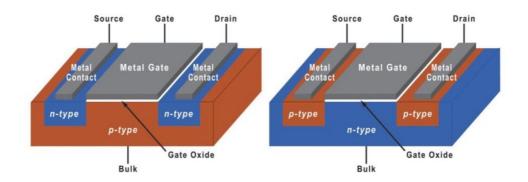

Another factor of variation found a lot in MOSFETS is the one that de- pends on the type of material used for the construction of the device including:

- The doping that is introduced in the materials usually has variations due to the dose, angle, energy and other types of variables that are taken into account when making the ion implantation. It is necessary to analyze the technology that is being used, since these deviations can cause losses in the adaptation of NMOS devices against PMOS. This can generate cases in which the variation is found within the wafer and the transistor array that are operating.

- Deposition: These types of changes in material parameters affect the variation in resistance generated at the transistor contacts.

Figure 1.2: Devices Material Variation.

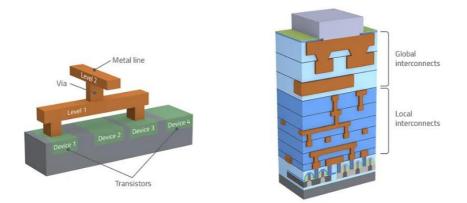

#### Interconnects Geometry

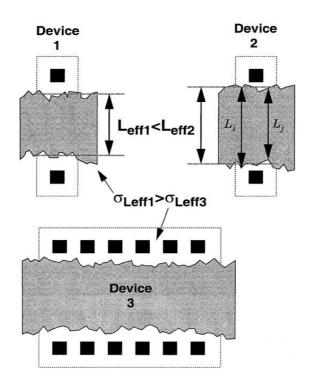

Following the analysis of the parts of a circuit where variability can be witnessed we find the interconnection geometry where we have the main effects on:

• Line width and line spacing: There are deviations in the width of the lines this is due to the effect of photolithography. The line width directly affects the resistance observed at the input and output of the integrated, the line spacing in turn affects the

capacitance. This can result in de- creased performance and increased power consumption due to glitches.

- Metal thickness: The thickness of the interconnect metal is usually de- posited symmetrically and correctly on a wafer, however, a lot of variability is observed when changing the wafer for printing. Although printing on a single silicon wafer is symmetrical, significant changes in metal strength can be observed due to erosion.

- Dielectric height: In order to fabricate the dielectric, the oxide needs to be deposited and polished, however, this process can lead to high device variability. In addition, the chemical-mechanical polarization process (CMP) causes variability in chip performance because the effective density of the topology changes in different parts of the wafer.

Figure 1.3: Interconnects Geometry Variation.

#### Interconnects Material

When talking about the interconnection of the devices we must also take into account the material with which they are made, since the following sources of variability can be found:

- Resistivity of the material: Depending on the material used, the resistance of the material changes. The moment where more variation can be observed is when changing wafers.

- Dielectric constant: This type of variation depends on the deposition process, however, this is usually very well controlled.

- Contact and via resistance: This is the largest source of variability as it is very sensitive to the printing process, and a random change is observed if the printing is changed from wafer to wafer.

Figure 1.4: Interconnects Material Variation.

The impact of variability is expected to be of great importance for future technologies (Hoefflinger, 2012), making this type of parameter variation an unavoidable feature in VLSI circuits. This means that it will be more difficult to estimate with certainty the exact performance and power consumption of a specific

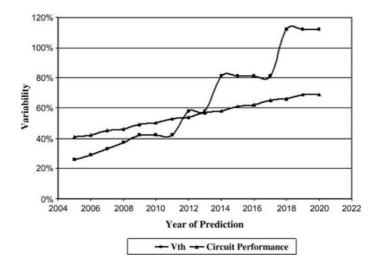

circuit. This is because variations in the physical parameter of the devices will greatly affect the electrical parameters. From Fig.1.5 it can be seen that the variation in the devices increases over the years. The threshold voltage parameter (V(th)) and the IC performance are the most affected, these mea- surements were performed by analyzing the delay generated in the leads and the integrated ones in the work reported in (Hoefflinger, 2012).

This uncertainty when designing integrated circuits means that the worst case scenario is always taken into account, the point at which it would be working below the optimum operating point. To give an example we could consider a thousand processors that were designed to operate at a frequency of 600 [MHz], if the manufacturing process has a variability of 10 % that affects the performance of the circuit. With these conditions if measurements of the devices are made to know the maximum operating frequency, we would find a Gaussian distribution centered at 600 [MHz] and a standard deviation of 20 [MHz]. If we interpret these results, we realize that only half of the processors manufactured operate at the maximum required

frequency. Therefore, the true operating frequency at which we could work is 540 [MHz], so that all devices can be used and potential processing time errors can be avoided.

Nevertheless, this is not all bad, as these types of variations are very useful for the design of physical unclonable functions, which promise to be a very interesting solution for cryptography. Being the main answer that could help the security problems faced by embedded systems (Daihyun Lim and Lee, 2005).

### Design of a Physically Unclonable Function

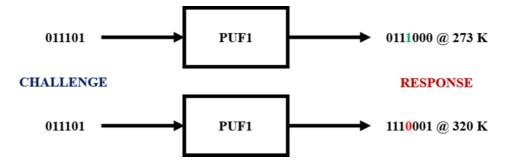

It is considered to be physical unclonable function when a cryptographic system is embedded in a physical object such as a silicon chip. This system must be able to receive an input signal which is processed and generates an output signal. The output will be known as response (R) and the input will be called challenge (C). It is necessary to mention that this system must be robust and difficult to clone, even considering the worst case which would be when the organization of the components of this system is known (Halak, 2018).

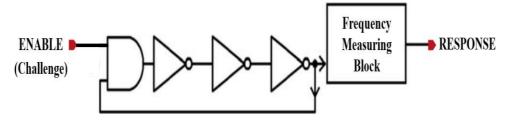

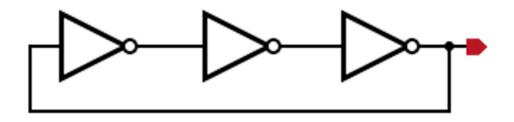

The basic example with which the design of this type of integrated circuits, the PUF, started is the ring oscillator shown in Fig.1.6. If we analyze this figure, we can see that the oscillator starts to work when it receives a logic 1 in the enable signal. Then, depending on the number of inverters and the physical properties of the technology used for the design of this circuit, there will be an oscillation frequency. This type of oscillator-based PUF only needs a challenge (enable signal) to generate a response (oscillation frequency). What is interesting is that due to the variation of manufacturing processes as we saw before causes a disorder in the semiconductor devices used in the

circuit. Causing this PUF in the response to have different oscillation frequencies when implemented in different devices. All these random responses can be used as a unique hardware signature for each physical implementation of this function. Thus achieving non-clonability, since all frequency variations encountered are not due to some software component. In fact, it is all inherent in the manufacturing process due to the lack of control over the geometry and materials used in the devices (Halak, 2018).

Figure 1.6: Conceptual Ring Oscillator PUF device.

Although the term PUF is relatively new, the thought of identifying objects based on physical properties is not. If we look back through history, some civilizations such as the Babylonian civilization used fingerprints to pre- vent counterfeiting. The way business was conducted at that time was quite interesting, since contracts were signed on clay using the fingerprint to verify that the two parties are the real ones (Xi, 2011). Nowadays, "uniqueness" has been used mainly to identify physical objects, such as nuclear weapons in the cold war. All nuclear warheads are identified by spraying a thin coating layer of a material that endows the object with unique light-reflecting characteristics. These nuclear warheads are then placed under the same light and, due to the imperfection in the coating material layer, generate a unique reflection pattern for each weapon (McFate, 2022).

Figure 1.7: Fingerprinting as a physical method of cryptography.

From these two examples we can say that to design a physical unclonable function it is necessary to have two components. The first is to have a physical disorder that is inherent to each object, the second is to generate a method to evaluate, classify and store this disorder.

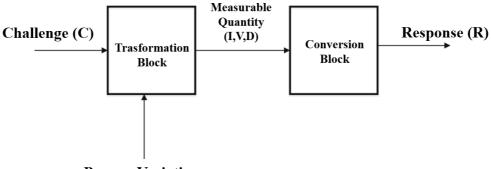

Modern integrated circuits have a large number of physical disorders. Since they arise in the process of manufacturing variation, therefore the first ingredient is easily obtained. However, the most difficult thing is to be able to transform this physical disorder into a measurable electrical quantity. The three electrical parameters that can be quantified in an integrated circuit are: current (I), voltage (V) and delay (D). The rest of the measurements that can be calculated are derived from these parameters, for example, the resistance that exists on a conductor is calculated with the voltage drop that exists at its ends divided by the average current that passes through it. In addition, in a PUF circuit it is desired to provide a response that is different for each applied challenge. Taking into account that in this era we live in a digital world, the response provided by the PUF must be digital. For this reason, if we consider the two main requirements of the silicon PUF, we will have the following:

• Considering the semiconductor technology and understanding how the variability of

the manufacturing process works, PUFs need to be able to transform these variations into measurable electrical quantities such as current, voltage or delay (Halak, 2018). PUF circuits need to be able to transform these variations into measurable electrical quantities such as current, voltage or delay.

• Every PUF circuit needs to transform its measurable electrical quantity into a digitally quantified response, i.e. a binary response (Fournel, 2016).

**Process Variation**

Figure 1.8: Architecture for silicon-based PUFs.

Understanding the above two requirements, an architecture that all silicon PUFs must follow can be proposed as shown in Fig.1.8. By comparing Fig.1.6 and Fig.1.8, we can understand that the oscillator is the transformation block and the frequency measurement block is a conversion block. The first block (transformation) is in charge of converting the challenge and the process variation of technology into a measurable electrical quantity. The second block (conversion) is responsible for converting the measurable electrical quantity into a binary value, i.e., the system response (Halak, 2018).

The above representation of the topology of a PUF allows us to have greater facility at the moment of reusing or designing new circuits. This is mainly because we

can perceive the design of a PUF as the construction of two separate blocks. There are currently some examples of designs for transformer and converter blocks in the literature. To give an example of the state of the art for the transformation block we would have: analog digital converter (DC/AC), ring oscillators, current sources, among others. In the conversion block we can find the following circuits: analog to digital converter (AC/DC), time to digital converter, phase decoders, comparators, among others (Halak B. a., 2008), (Nawi, 2016).

PUF devices are classified. Due to the need for measurable electrical quantity, we would have PUFs based on current, voltage and delay. It is necessary to understand that there are PUFs that do not exist within these three categories. To understand this better we would have as an example the devices that are based on the variation of the conduction current or threshold voltage. However, the categorization based on current, voltage and delay provides in a more intuitive way the different design techniques that can be used (Halak B., 2018).

Figure 1.9: PUF novel solution for cryptography.

### **Delay Based PUFs**

This type of cell is responsible for transforming the variations of the integrated circuit into delay, and then transforming it into a binary response. The first proposals of PUF structures were based on this type of cells, so there are several solutions using this parameter. If we analyze the literature, we can find architectures based on arbiter (Lin, 2012), ring oscillators (Yin, 2010) and those based on an asynchronous structure (Suh, 2007). In the following, we describe the operation of these types of cells working with the delay response.

Arbiter

Figure 1.10: A single challenge arbiter PUF.

The structure shown in Fig.1.10 is known as an arbiter-based cell. It is called this way because if we look at the composition of the cell it consists of two parts. The two digital paths that must have the same nominal delay, and the arbiter at the output converts the delay into a digitized response. This cell works by applying an enable signal at the input, which propagates through the two digital paths. As the delayed signals from each of the paths arrive at the inputs of the arbiter, due to intra-die variability either of these signals can be the one that determines the final value of the circuit. The arbiter discretizes the output signal by giving a logic "1" or "0" depending on which path was the fastest. When this circuit is replicated on multiple chips, the

response changes due to inter-die variations. In other words, this response is unique for each implementation, so it can be considered a hardware signature (Halak B., 2018).

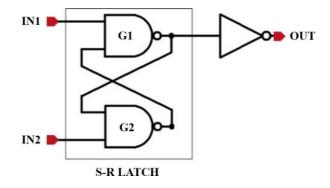

Figure 1.11: Circuit diagram of an arbiter based on an S-R latch.

Then, we will talk about the arbiter, normally for this structure is usually used a Set-Reset latch. This latch is normally built as shown in Fig.1.11 with two cross-coupled gates. The operating principle of this circuit is as follows:

- If both inputs have a low logic level, the output has a low logic level as well.

- If only one of the signals changes state to a logic high level, the response will change its state accordingly and will be blocked. To better explain this process, we look at Fig.1.11, and assume that inputs IN1 and IN2 are in a logic low state. In the first case IN1 changes to a logic high state, causing the output (OUT) to also change its state from low to high and remain at this value even though IN2 changes. Now if we analyze the second case where instead of IN1 it is IN2 that changes its state from low to high. The output will remain in a low logic state because this is how the combinational circuit is described, in the same way as for the previous case the signal is blocked, but in the low logic state.

- If both signals arrive at the circuit in a high state, but there is a small but significant

difference in their arrival. The output will assume the value of the signal that arrived first, i.e., logic "1" if IN1 arrived first or logic "0" if IN2 arrived first.

• Special case: if the two signals arrive in a high logic state, but with almost zero delay difference, the output enters a meta-stable state.

$$V(t) = V_0 e^{t/\tau}$$

1.1

The meta-stability is stopped approximately when gates G1 or G2 reach the threshold voltage, therefore in equation 1.1 we could substitute the values by having:

$$t = \tau Ln(V_{th}/V_0)$$

1.2

Taking into account the probability analysis, we can observe that if we have a meta-stability event at t = 0, the probability of having a meta-stability event in a longer time is:

$$P_m(t) = e^{-t/\tau} 1.3$$

Theoretically, one could calculate precisely the moment at which the metastability stops. However, to do this requires precise knowledge of the geometry of the circuit, as well as the voltage levels being delivered by gates G1 and G2. All the information needed to do this analysis is very complicated to obtain in practice. As an example, we would have the scenario where it becomes complicated to find out the state of the arbiter; since it is not possible to know if the output is a logic zero because the IN2 signal arrived first or if we are in the case of meta-stability (Halak B., 2018).

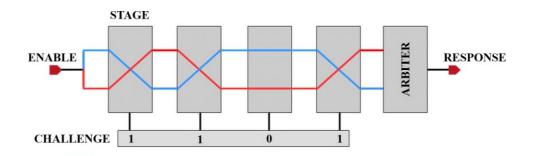

One of the first example that can be found in the literature related to the arbiter-PUF is the one proposed in (Daihyun Lim and Lee, 2005). In this paper, it was suggested to use a design that implements multiplexers connected in series for the logic paths. Each multiplexer has a selection signal, which allows to choose the digital path to be followed. Thus, achieving with this structure that depending on the challenges that are placed in the cell, the path or the delay that can be observed at the output is configured. The number of bits that the challenge will have depends on the number of multiplexers connected in series that the circuit has. Each bit pattern given to the challenge gives a unique configuration to the digital path to be used. Therefore, the response observed at the output is unique for each challenge given to the PUF. The architecture implemented in this paper is shown in Fig.1.12 below.

Figure 1.12: Structure of a multiple bit challenge arbiter PUF.

The maximum number of challenge/response pairs that the arbiter-PUF proposed in [1] is obtained by analyzing the number of gates or stages (k) connected to a challenge. The equation that determines the number of responses that can be obtained based on the size of the challenge is the following:

The structure that was proposed for the arbiter in the PUF cell of (Daihyun Lim and Lee, 2005) is based on a transparent latch. Nevertheless, the authors reported that due to the asymmetry of the latch, the correct predictability of the response was greatly affected. This is mainly due to the fact that the latch has to favor one path, reason why most of the responses are "0" instead of "1". To be precise with the article, 90% of the answers were a low logic level, which is not what is desired for this type of circuits. However, the authors made proposals to systematically change the delay of the logic paths. This in order to reduce this problem and to have a 50% probability of obtaining a logic "0" or a logic "1". In addition, these methods make the PUF intrinsically more predictable, since they are not based on a physical disorder but rather on the designed variations.

The main difficulty in achieving a fully symmetrical chip design is that the designs are done with automated software. These tools just place the components (standard cells) and interconnect them depending on what is favorable for area, power consumption or performance. These tools do not take into account the symmetry required for this type of cells, which depend on their homogeneity when designing them. This limits the degrees of freedom that the designer has to control the behavior of the circuit. Therefore, it is necessary to use tools that allow the manual design of the PUF's, in order to ensure the maximum possible symmetry in the trajectories of the delays (Halak B., 2018).

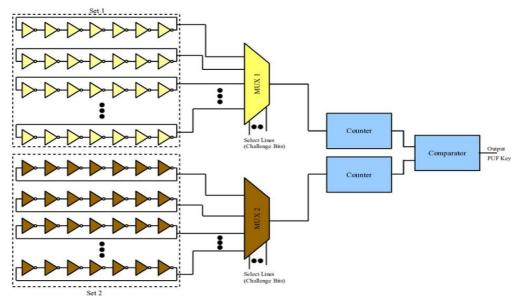

#### **Ring Oscillator PUF**

The first appearance of this ring oscillator-based structure was composed of: two multiplexers, two counters, a comparator and a number (k) of ring oscillators (Suh, 2007). The basic structure of this circuit is presented in Fig.1.13, the operation of this PUF is quite simple and consists of the following stages:

• Ring oscillators have a unique frequency that depends on the characteristics of the inverters.

- The two multiplexers are intended to select the two ring oscillators to be compared.

- The counters are used to count the number of oscillations that RO generates in an interval of time.

- The comparator determines which ring oscillator had the highest frequency and thus determines the output value of either logic "0" or "1".

Figure 1.13: Structure of ring oscillator PUF.

Similar to what was observed in the arbiter-based PUF, this cell still has the need for the ring oscillators to have the same nominal delay. However, this architecture allows us to have a response without using an arbiter, thus eliminating the meta-stability problem. Thus giving a higher reliability to the response obtained from this PUF (Suh, 2007).

The maximum number of challenge/response pairs (CRP) is strongly linked to the architecture. In this specific case of the RO-based PUF we can determine that the CRP depends on the number of ring oscillators implemented. So, the equation that determines the CRP would be given by the following expression, where k is the number of RO in the architecture (Suh, 2007).

$$CRP = \frac{k(k-1)}{2}$$

1.5

#### Self-timed Rings PUF

This is another type of architecture proposed for PUFs that base their response on delay, the idea is described in better detail in (Yakovlev, 2012). Its structure is mainly based on the classical ring-oscillator PUF architecture shown in Fig.1.13; however, it uses self-timed cells instead of classical inverters. This type of self-timed cells implements the Muller's C element, which is described in the article as a fundamental building block for asynchronous circuits. A circuit using the C-element and based on the CMOS logic family can be seen in Fig.1.14 below. The principle of operation of this cell is simple and is as follows.

- The output acquires the logic value "1" or "0" when the two inputs have the logic value of "1" or "0" respectively.

- If the respective values are not present, the output remains in the previ- ous state, i.e., it does not change.

Figure 1.14: Muller-C element.

Fig.1.17 shows a clear example of a self-timed ring (STR), it can be seen that this structure consists of three stages. All the stages are constituted by a C element and an

inverter. The connection of these elements is interesting, since the inverter is connected in reverse (R) with the C element and the second input of this cell is connected with the forward stage (F) (Yakovlev, 2012).

Figure 1.15: Three stage self-timed ring (STR).

In order to better understand how this structure works, the concept of bubbles and tokens must be introduced. We can say that an STR stage has a bubble if and only if the output is equal to the output of the previous stage. The opposite case is when it is considered that there is a token, since the output of the STR is different from the signal of the previous stage (Yakovlev, 2012).

Figure 1.16: Token and bubble movement.

Since self-timed rings have a particular operation, the conditions for this circuit to oscillate are a bit more complicated than the typical RO. The first requirement is that the number of stages the STR has must be greater than or equal to three. The second condition is that the sum of tokens and bubbles must be equal to the number of stages the

STR possesses. To better understand this, the equations underlying these oscillation conditions are described (Yakovlev, 2012).

$$STR \geq 3$$

1.6

$$STR = N_b + N_t$$

1.7

What makes this self-timed ring structure interesting is the increased robustness of the PUF response to environmental variations. Obviously, this benefit comes at a high cost in terms of the silicon area used, it should also be added that this type of structure can suffer from blocking states (Yakovlev, 2012).

Figure 1.17: Smart PUF based on self-timed ring structure.

#### Current-Based PUFs

This type of architectures have the ability to convert the variation of manufacturing processes, in a current quantity that can be measured by different circuits. Like all PUFs, this response must be completely digital in a binary system. Two structures based on this type of solution are presented below. The first solution focuses on using the current obtained from transistors that are working in the subthreshold region. The second proposal attempts to capture the leakage currents that exist in a dynamic random access memory (DRAM).

#### Current-Based PUFs Using Transistors Arrays

In the literature it is possible to find some solutions that are based on the current to generate PUFs, however, one of the first proposals that can be found is the following (Kalyanaraman, 2013). This design is quite interesting since it employs MOSFETS, which is the reason why it is possible to take advantage of the exponential current that is present when the device works in the subthreshold region. In order to operate in this regime it is necessary to use the threshold voltage ( $4V_{th}$ ) and the gate-source voltage ( $V_{gs}$ ). This in attempt to increase the unpredictability of the PUF operation, the design of this architecture is presented in Fig.1.18 below.

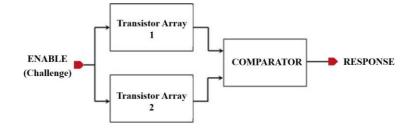

Figure 1.18: A current-based PUF.

The principle of operation of this architecture is simple and is described as follows:

- The challenge signal is applied to two identical arrays of transistors.

- The challenge signals select a number of transistors that send their response to the output of the matrices.

- The outputs of the matrices present a current value, which is compared in order to have a binary response.

The number of challenge/response pairs is of high importance for the PUFs, as well as those based on delay, these also depend on the architecture being used. Since this architecture depends on matrices, the variables k and n are defined as the number of rows and columns that exist in the structure, respectively. Therefore, the expression that defines the CRP is the following (Halak B., 2018).

$$CRP = 2^{kn} 1.6$$

Several ways to realize transistor arrays such as the one proposed in the paper (Kalyanaraman, 2013) can be found in the literature. However, this design has some shortcomings, such as the low voltage at the output of the array. Which makes it difficult to develop a comparator that is robust enough to determine a good comparison. Animproved version for this transistor array was proposed in (Mispan, 2015). A simplified block diagram is presented in Fig.1.19 below.

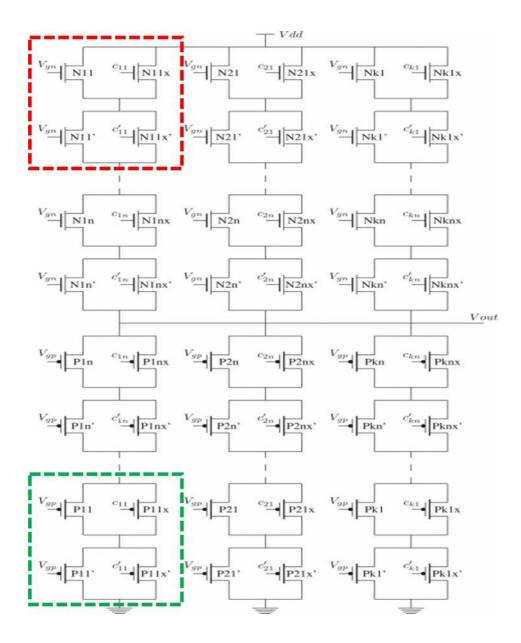

Figure 1.19: Circuit schematic of the TCO unit array.

The matrix shown in Fig.1.19 is made up of k columns and n rows, everything is built based on the unit cells that are highlighted in the image. By analyzing the unit cells we can realize that it is built with two transistors in parallel. One of these transistors has been designed with the minimum size allowed by the technology, in order to maximize the variability observed in its threshold voltage. This transistor is of

critical importance to the unit cell and is referred to as a "stochastic transistor", e.g., in Fig.1.19 it would be the  $N \, 11x$  transistor. The function of the second transistor is to operate as a switch, working as a block for the stochastic transistor when it is on, or to allow to deliver the response when the stochastic transistor is off. We can find as an example of the second transistor in Fig.1.19 the  $N \, 11$  device, we will know it as "switch transistor" (Mispan, 2015).

For each unit cell a single challenge bit is given for both the NMOS transistors and their symmetrical complement PMOS. For example, if we look at Fig.1.19 we can notice that the challenge bit C11 applies to the components marked in green and red.

In the following, we will analyze the fundamental behavior of the matrix and how it detects the values. If the challenge signal is a logic "1" the switch transistors will behave as follows, NMOS and PMOS would be on and off respectively. However, the stochastic transistor will always have a contribution to the response regardless of whether the challenge is "0" or "1". This is because the inverted and non-inverted versions of each bit are connected to the stochastic transistor. This means that every second stochastic transistor is part of the network, regardless of the binary data that is carrying the challenge signal. This architecture is defined in the literature as "Two Chooses One" (TCO). Finally, the output provided by each matrix depends on the current accumulated by the transistors (Mispan, 2015).

Due to the inherent intra-die variations, it is possible to ensure that the output voltage of one of the arrays is slightly higher than the other. Consequently, dynamic comparators can be used to find this difference, e.g. Op- Amps (Mispan, 2015).

In order to build a current-based PUF, several parameters such as those shown in the previous example must be taken into consideration. First, the correct voltage must be applied to the gates of the stochastic transistors to allow them to operate in the subthreshold region. Moreover, the switch transistors must deliver a negligible subthreshold current and at the same time they should provide small ON-state resistance. Furthermore, to achieve good performance in unit cells, the dimensions of the switch transistors should be at least ten times those of the stochastic transistors. It must also be understood that the difference in the voltages observed at the output of the arrays has to be sufficiently large to be well detected by the comparator thus avoiding unreliable responses (Halak B. , 2018).

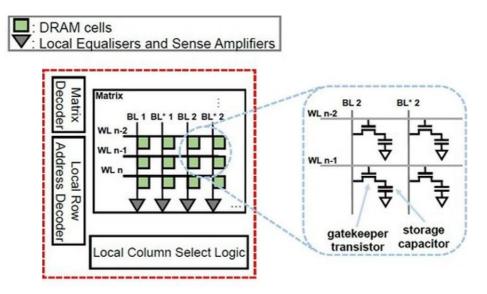

#### Current-Based PUFs Using Dynamic Random Access Memories

The basic structure of a DRAM cell is constituted by a capacitor along with an access transistor as shown in Fig.1.20. Each basic cell has the capacity to store a single bit of information. Without periodic updates the leakage current from the access transistor may cause the value to be lost. The velocity at which the capacitor is discharged is directly proportional to the leakage current, which depends on the technology in which the design was manufactured. The latter is strongly affected by process variations indeed, cells belonging to the same wafer exhibit different leakage currents. In the literature we can find innovative ideas on how to use memories as PUFs, however, we will use as a basis the work proposed by (Xiong Wenjie, 2016) in which the unique behavior of value decay in DRAM cells induced by process variability was exploited for PUF applications:

- First we need to select the region of the memory that we want to behave as a PUF, this is achieved by defining the initial address and the size we want to analyze.

- The update function is then disabled for this specific part of the memory.

- We proceed to write an initial value to be stored in this region.

- Then access to all cells in the previously selected region is disabled for a defined time

(t). During this period of time the load of each unit cell decays proportionally to the leakage current that each cell has.

- After the time that the memory section was disabled, a reading is made to verify which values remained stored. This response is the value given to the PUF response.

- To conclude the process, the previously selected region is returned to normal operation and becomes available for the operating system again.

## Figure 1.20: DRAM.

Similar to the rest of PUFs, its value of challenge/response pairs depends on its architecture. For this specific type of array, it depends on the size of the memory section selected, and the decay behavior of the DRAM must also be considered. To understand this better, we could imagine the case in which in a DRAM memory there are R spaces reserved to structure the PUFs. Where it is possible to have different N decay periods for each selected space, which would give a unique response for each chip. The expression used to calculate the CRP for this architecture is shown below (Xiong Wenjie, 2016).

$$CRP = RN$$

1.9

As with all integrated circuits, if you want to implement this DRAM- based architecture, there are several points to consider. The first point to take into account is the careful study of the DRAM memory behavior, in order to understand which are the decay times of the unit cells. To understand this more objectively, let's look at the following case: if the leakage current of the DRAM cells is very high and the discharge time is very long, there is a risk of losing all the data. It is also possible to consider a totally opposite case, where the load decay is too slow and when analyzing these data there is no variation. For both cases the behavior of the PUF would be too predictable, so this design would be a bad implementation for some types of memory (Halak B. , 2018).

## Voltage-Based PUFs

This type of PUFs is responsible for transforming manufacturing process variations into voltage values that can be measured and quantified to have a digital response. Two architectures that are quite strong in the current literature of voltage-based PUFs are briefly presented below. The first solution uses as base cell a static random access memory (SRAM), the second circuit on the other hand uses as base a S-R Latch (Halak B., 2018).

4 0

### SRAM PUFs

This type of solution, which is based on the use of static random access memories, is found in the literature as the first approaches to a PUF that bases its response on voltage measurement. Initially, this proposal was used in FPGAs in order to generate encryption keys, this type of security is specific to the device and is used to encode bit streams before storing them in an external memory. This specific proposal focuses on data protection when the adversary has the ability to decrypt the storage bitstream. These PUFs fulfill the objective of preventing the attacker from reusing a bitstream to program other FPGAs (Guajardo Jorge, 2007).

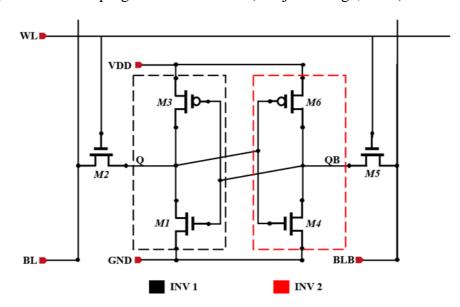

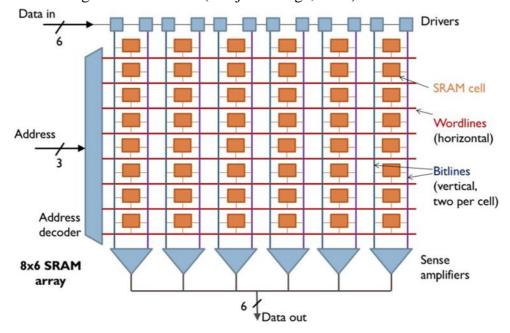

Figure 1.21: 6T-SRAM Schematic.

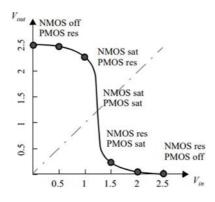

We will now discuss the behavior of an SRAM-based PUF, for which it is necessary to understand the basic circuitry of this type of memory. Fig.1.21 presents the basic architecture of the six-transistor SRAM, which consists of two cross-coupled inverters and two access transistors. The inverters can be in two logic states "1" or "0", in order to reach these values it is necessary to use the M2 and M5 transistors. The access transistors M2 and M5 receive the signals from the voltage lines BL and BLB, taking into account that the voltage levels received by these lines must be complementary. This means that if we want a correct storage operation, BL and BLB must receive logic "1" and "0" respectively or vice versa in order to access the cell correctly. The inverters are going to drive inverse states, in other words if we look at Fig.1.21 we have that INV 1 and INV 2 drive Q and QB respectively. The voltage line that we know as WL is the one in charge of selecting the operation that we are going to perform with the memory such as: storage, read and write (Guajardo Jorge, 2007).

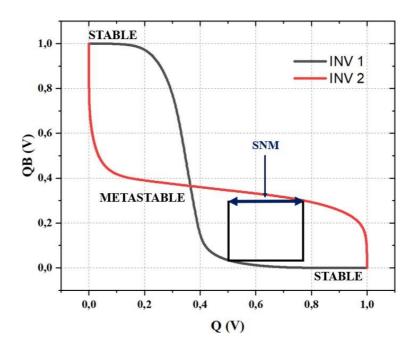

Figure 1.22: Characteristics for SRAM.

When the SRAM cell is biased to the correct voltage values by the access transistors, the cross-coupled inverters start a "power struggle". The winner of this contest is decided by the difference in the MOSFETS used by the inverters. As can be seen in Fig.1.22 this ends up with three possible operating points for the memory, where two of these states are stable and the third is considered metastable. In the hypothetical case where all the transistors that make up the SRAM cell are perfectly

coupled, in theory the state of this memory would be metastable for all time. However, in real life due to manufacturing variation processes, even though at the circuit level the whole structure is designed perfectly coupled. Always one of the two inverters in the SRAM will have a higher conduction current, which is why it is possible to define the initial starting value of the cell (Guajardo Jorge, 2007).

Figure 1.23: SRAM Memory Array.

The basic cells of SRAMs usually have an initial state, which is obtained at the specific moment of turning on these memories. This specific feature is what allows us to use this type of devices for the creation of PUFs. Since the reading of the resulting PUF value depends on the size of the memory, we can say that the CRP is proportional to the size of the device array. In other words, the challenge is the address of the memory to be read and the response is the read values of the beginning of the addressed cells. To understand this more objectively let's consider the following example, for a 64 megabits byte- addressable memory we have 8 megabits of CRP.

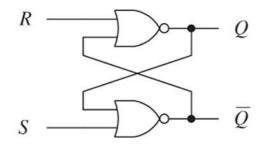

### Latch-Based PUFs

This is another type of design that uses voltage variation as a basis for the generation of PUFs based on relatively simple circuits. In this design, it attempts to take advantage of the small variability of threshold voltages that the NOR gates coupled together have (Stanciu, 2016). Fig.1.24 presents a basic schematic of the design of this type of circuit. The principle of operation of this cell is identical to that described for the arbiters in lanches using delay-based PUFs. What is important to mention is when the cell enters a metastable state, since after a certain time a logic "1" or "0" can be obtained. These logic values will be strongly related to the variations in the driving capability presented by the gates.

Figure 1.24: SR Latch.

As simple as this circuit may seem, it is not so reliable for the development of a PUF. In order to operate as a cryptographic device, it needs to enter a metastable state. Therefore, it is quite difficult to determine the minimum time it takes for the circuit to overcome this state. In addition, these types of cells are often very susceptible to response variations due to changes in the conditions of their environment (Stanciu, 2016).

# Metrics of PUF Devices

In the previous sections of this chapter we discussed the design of PUFs and how to use their physical variability to generate safety systems. However, we have not yet discussed the metrics that these cells must satisfy to guarantee the quality of a PUF design. In addition to the qualities it must have to be suitable for a specific application. For this reason, in this section we will introduce the four metrics with which the physical unclonable functions are evaluated. Where we find the parameters of: uniqueness, reliability, uniformity, and tamper resistant. It is also necessary to mention that the Hamming distance and Hamming weight are used for the calculation of these metrics. For this reason, below you will find the definition of these concepts (Maiti Abhranil, 2013).

*Hamming Distance:* The Hamming distance d(a, b) between two words  $a = (a_i)$ and  $b = (b_i)$  of length n is defined to be the number of positions where they differ, that is, the number of (i)s such that  $a_i \neq b_i$ .

*Hamming Weight:* Let 0 denotes the zero vectors: 00...0, The Hamming Weight HW (a) of a word  $a = a_1$  is defined to be d(a, 0), the number of symbols  $a_i \neq 0$  in a.

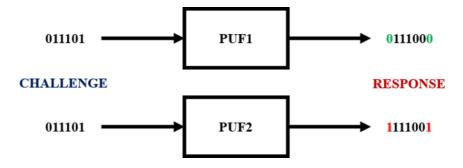

#### Uniqueness

This is a metric to determine the ability of a device to have a unique response. It is a measure in which the ability of a PUF to behave in a unique and distinguishable way from other PUFs that have the same structure on other chips is determined (Maiti Abhranil, 2013).

$$HD_{INTER} = \frac{2}{k(k-1)} \sum_{i=1}^{k-1} \sum_{j=i+1}^{k} \frac{HD(R_i(n), R_j(n))}{n} * 100\%$$

1.10

To better understand what equation 1.10 is trying to explain, let us consider the example shown in Fig.1.25. In this example we can observe two PUFs receiving the same challenge (011101), to which each device gives a different response. If we analyze the responses given we have the following PUF 1 = 0111000 and PUF 2 = 1111001, where we can see that the two responses differ by 2 bits. With this we can say that out of 7 bits of response 2 bits change therefore the PUFs are unique. However, the inter-chip Hamming distance is small as it is 28% and to ensure that these devices are safe we are looking for a 50% variation between the response of the chips.

Figure 1.25: Uniqueness evaluation of a PUF.

#### **Reliability**

This metric determines the PUF's ability to deliver the same response for a fixed challenge even under different environmental conditions (i.e., temperature and voltage variations). The concept by which this metric is evaluated is the intra-chip Hamming distance (Maiti Abhranil, 2013).

$$HD_{INTRA} = \frac{1}{k} \sum_{i=1}^{k} \frac{HD(R_i(n), R'_i(n))}{n} * 100\%$$

1.11

$$Reliability = 100\% - HD_{INTRA}$$

1.12

.....

In order to have a clearer understanding of this metric, we will consider the example shown in Fig.1.26. As we can see, a PUF is given the same challenge, but its response is evaluated at different temperatures. Ideally, the Hamming distance inside the chip should be 0%. This would guarantee 100% device reliability. However, in real life achieving this goal is very complicated, that is why in Fig.1.26 we have the case where changing the temperature from 273K to 320K the response is modified. This causes the on-chip Haming distance to be 14% and the final PUF reliability to be 86%.

Figure 1.26: Reliability evaluation of a PUF.

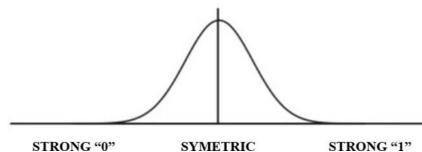

## Uniformity

This is a metric to determine the unpredictability of the responses that a PUF can give. To calculate uniformity it is necessary to use the concept of Hamming's average weight, where in order to have a completely random response, this value needs to be 50%. In other words, the objective is that the proportion of logic "1" and "0" should be the same in the PUF output (Maiti Abhranil, 2013).

Figure 1.27: Uniformity response of a PUF.

Uniformity

$$= \frac{1}{k} \sum_{i=1}^{k} r_i * 100\%$$

1.13

## Tamper Resistance

This is a metric that attempts to determine the resistance of a design to manipulation by adversaries. Ideally a PUF changes its response completely if the design or structure is modified by any attack on the device. This can be determined using the Hamming distance between the original chip and the tampered chip. The mathematical expression with which this value can be calculated is given below (Maiti Abhranil, 2013).

$$HD_{AVE} = \frac{1}{CRP} \sum_{L=1}^{CRP} \frac{HD(R_i(l), R'_i(l))}{n} * 100\%$$

1.14

To determine that a PUF is tamper resistant the response it should exhibit after the Hamming distance calculation is 50%. Since the response of the PUF is completely different from the one it should have before the manipulation (Maiti Abhranil, 2013).

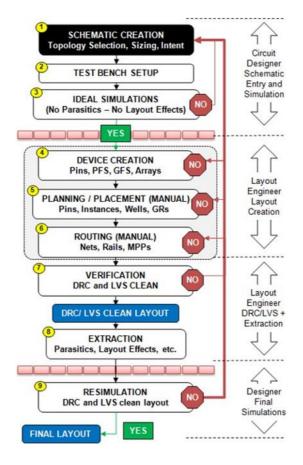

#### DEVELOPMENT AND SIMULATION METHODOLOGY

This chapter will describe the design and simulation methodology used for the development of the PUFs. This type of integrated circuits that seek to exploit physical imperfections due to manufacturing variations to generate a hardware signature, strongly depend on the symmetry of the design. For this reason, it was decided to use the full custom methodology for VLSI circuits. The following is a brief description of this design method and the implications necessary for its correct execution.

## Full custom metodology

The fully custom design of integrated circuits is of great importance, as it allows the designer to place each transistor and its connections according to the design specifications. The real benefit of using this technique is that maximum performance can be achieved, silicon area can be minimized and power consumption can be improved. However, its application is too laborious and the development time is very long. For that reason, this design technique is limited to integrated circuits that need very efficient performance and mass production. In the following, we will describe the necessary requirements for a fully customized design such as: the transistor technology, the development tool and the complete flow of this methodology

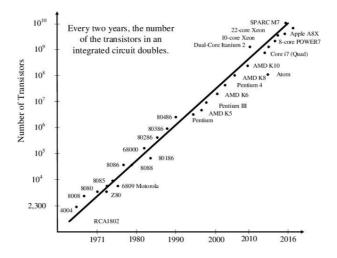

## Technology

The transistor technology node refers to the specific semiconductor manufacturing process including design rules. Throughout history the process node name refers to the physical characteristics of a transistor, such as channel length. Lately, due to various marketing issues, this number has lost its meaning. Because the name given to newer technology nodes does not refer to either the gate length or the average pitch. The main reason for maintaining node scaling is Moore's law. Moore's law states that in order to achieve a doubling of transistor density in a specific area, the poly-pin contact (CPP) and minimum metal pitch (MMP) have to increase by 0.7 times between technology nodes. Generally when reference is made to a smaller technology node, smaller device size is usually meant. This means that more transistors can be fabricated in a smaller area, with the benefits of improved performance and reduced power consumption.

Figure 2.1: Evolution of the number of transistors every two years according to

#### Moore's Law.

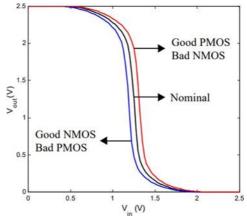

Taiwan Semiconductor Manufacturing Company (TSMC) is the world's largest chip manufacturer. Founded in 1987, TSMC was the first company to focus exclusively on semiconductor devices. Although TSMC offers several silicon wafer product lines, it is best known for its logic chip production area. For this thesis and the design of the PUFs, TSMC's 180nm technology node was used. In particular, for the PUF topologies considered in this the- sis, NMOS with regular threshold voltage (RVT) and PMOS with medium threshold voltage (MVT) were used.

### Development software

Technological Computer Aided Design (TCAD) is one of the automation branches of electronic design with which the fabrication of semiconductor de- vices and their behavior is modeled. Technology files and design rules are the most important elements for the design of integrated circuits. These software present high accuracy in terms of the manufacturing process technology, variability and operating conditions of the integrated circuit. They are extremely important to accurately determine the performance, yield and reliability of the chip. For this reason, modeling and simulation are a very important aspect in the evaluation of the integrated circuit.

The TCAD takes into account the physical description of the devices considering their configuration, material-related properties and the connections that exist between the physical and electrical model. Since physics-based device modeling is the fundamental part of IC development, TCAD aims to quantify the understanding of the technology. The objective of TCAD is to quantify the understanding of the technology and to abstract that knowledge at the design level, including the extraction of parameters that support the development of the circuit at the electronic level. For this thesis we used the Cadence-Virtuoso TCAD focused on analog circuit design. The following is a brief description of how this software works and what can be done with it.

### 1. Virtuoso Analog Design Environment

This integrated circuit development environment provides the necessary capacity for the analysis, exploration and verification of a design based on the user's needs. This allows the designer to achieve all the requirements required for the development of the project, taking into account all the flow involved. This tool is used for the control, management and simulation of analog circuits. It allows the designer to flexibly select the level of customization desired in the integrated circuit.

Figure 2.2: Flow of custom design.

- First, it is necessary to select the technology to work with.

- Then, design circuit at schematic level using Cadence's schematic editor.

- The circuit is then simulated using the Cadence analog simulation environment. This is done in order to verify that the design is working as desired.

- Once the device specifications have been reached, the circuit is created at the physical level using the Virtuoso layout tool.

- The layout resulting from the implementation must be verified by some geometrical rules that depend on the selected technology. For this purpose, design rule checks (DRC) are used.

- Continuing with the flow, the electrical verification has to be performed, checking for short-circuit faults. This is possible by checking the electrical rules (ERC).

- Afterwards, it is necessary to verify the circuit's schematic and layout agreement. Checking that all devices and connections are correctly made, using the layout versus schematic (LVS) analysis.

- Consequently, it is necessary to extract a network that includes all the parasitic elements of the physical implementation. Using the Parasitic Layout Elements Extraction (PLE) tool.

- Finally, a simulation is performed considering these parasitic elements, in order to have a response that is very similar to real life and that we would find after printing. This last analysis is known as post layout simulation.

## 2. Analog Design Environment XL

The Analog Design Environment XL is an advanced simulation tool that incorporates Virtuoso. This platform supports comprehensive analysis of multiple designs and is therefore established as the standard in IC verification.

- Supports extensive verification of environmental conditions and operat- ing conditions.

- Analysis of multiple simulations, through testing under the operating conditions of the integrated circuit. Compiling all data in an easy-to-use database.

- It is capable of performing process variation simulations, corners, para- metric sweeps, Monte Carlo and reliability analysis.

- It allows quick debugging of the design by delivering a response that depends on the design stored in the system.

#### **PROPOSED SCHEMES AND RESULTS**

In the following chapter we will present the development of two PUF cells. The main point of interest is to understand the benefits of using a dynamic structure and a static structure. The static cell will have a voltage divider as its basis, the dynamic cell will have a ring oscillator as its main component.

# Metastable PUF bitcell

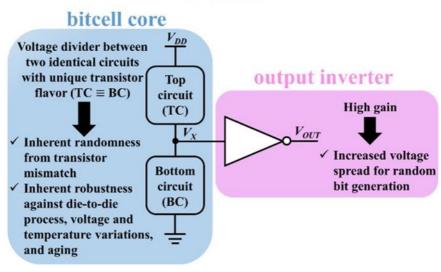

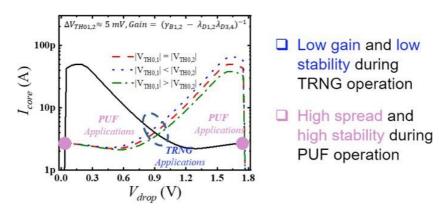

The bitcell described here belongs to the voltage based class. In particular, the circuit is based on a sub-threshold voltage divider between two nominally identical series connected sub-circuits (i.e., top circuit TC and bot- tom circuit BC with nominally TC  $\equiv$  BC) along with an output inverter for generating the binary response as illustrated in Fig.3.1. The circuital approach intrinsically guarantees randomness from transistor mismatch as well as robustness against inter-die process variations, environmental variations (i.e., voltage and temperature variations) and aging.

# **PUF** bitcell

Figure 3.1: Conceptual diagram of the proposed PUF bitcell.

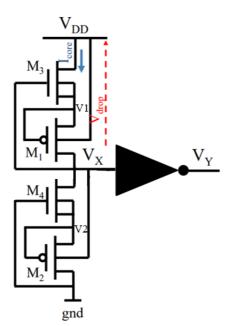

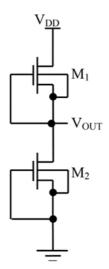

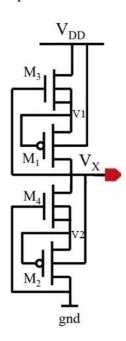

Fig.3.4 illustrates the transistor-level scheme of the analyzed bitcell which employs a four transistor (4T) sub-threshold voltage divider between two transistors (2T) sub-circuit. Each 2T block is composed of the series of negative-VGS NMOS (i.e.,  $M_3$  in the TC and  $M_4$  in the BC with nominally  $M_3 \equiv M_4$ ) with a reverse bodybiased PMOS (i.e.,  $M_1$  in the TC and  $M_2$  in the BC with nominally  $M_1 \equiv M_2$ ). From the same figure it is also necessary to point out that the body terminal of M<sub>3</sub> and M<sub>4</sub> is connected to the relative source terminal which required the use of deep-n-well regular-voltage transistor (RVT) while for zero-V<sub>GS</sub> biased PMOS (i.e., M<sub>1</sub> and M<sub>2</sub>) medium-voltage transistors (MVT) were used for achieving more variability. Both transistors in each 2T sub-block were upsized (i.e.,  $W_{1,2} = W_{3,4} = 5 \mu m$ ) while keeping low their channel length (i.e.,  $L_{1,2} = L_{3,4} = 250$  nm which corresponds to a minimum channel length for MVT transistors, M<sub>1</sub> and M<sub>2</sub>, and a channel length close to the minimum one for the RVT transistors,  $M_3$  and  $M_4$ ) to counteract the effect of the parasitic diodes associated to the use of deep-n-well transistors. Conversely, the output inverter was minimum sized because its task is only to digitize the voltage coming from the 4T voltage divider as well as to guarantee an high input impedance for electrically isolating each bitcell since the current flowing in the 4T-core is very small.

Figure 3.2: Metastability characteristic.