**UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ**

**Colegio de Posgrados**

**Design of a Dynamic Comparator with Self-adjustable Offset in CMOS

65nm**

**Tesis en torno a una hipótesis o problema de investigación y su

contrastación**

**Juan Pablo Cuenca Fernández**

**Marco Lanuzza, Ph.D.

Director de Trabajo de Titulación**

Trabajo de titulación de posgrado presentado como requisito

para la obtención del título de Master en Nanoelectrónica

Quito, 2025

**UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ**

**COLEGIO DE POSGRADOS**

**HOJA DE APROBACIÓN DE TRABAJO DE TITULACIÓN**

**Design of a Dynamic Comparator with Self-adjustable Offset in CMOS

65nm**

**Juan Pablo Cuenca Fernández**

Nombre del Director del Programa:

Luis Miguel Prócel

Título académico:

Doctor of Philosophy

Director del programa de:

Maestría en Nanoelectrónica

Nombre del Decano del colegio Académico:

Eduardo Alba

Título académico:

Doctor of Philosophy

Decano del Colegio:

Colegio de Ciencias e Ingenierías

Nombre del Decano del Colegio de Posgrados:

Dario Niebieskikwiat

Título académico:

Doctor of Physics

**Quito, Enero 2025**

## © DERECHOS DE AUTOR

Por medio del presente documento certifico que he leído todas las Políticas y Manuales de la Universidad San Francisco de Quito USFQ, incluyendo la Política de Propiedad Intelectual USFQ, y estoy de acuerdo con su contenido, por lo que los derechos de propiedad intelectual del presente trabajo quedan sujetos a lo dispuesto en esas Políticas.

Asimismo, autorizo a la USFQ para que realice la digitalización y publicación de este trabajo en el repositorio virtual, de conformidad a lo dispuesto en la Ley Orgánica de Educación Superior del Ecuador.

Nombre del estudiante: Juan Pablo Cuenca Fernández

Código de estudiante: 00333080

C.I.: 1104797343

Lugar y fecha: Quito, 27 de enero de 2025.

## ACLARACIÓN PARA PUBLICACIÓN

**Nota:** El presente trabajo, en su totalidad o cualquiera de sus partes, no debe ser considerado como una publicación, incluso a pesar de estar disponible sin restricciones a través de un repositorio institucional. Esta declaración se alinea con las prácticas y recomendaciones presentadas por el Committee on Publication Ethics COPE descritas por Barbour et al. (2017) Discussion document on best practice for issues around theses publishing, disponible en <http://bit.ly/COPETheses>.

## UNPUBLISHED DOCUMENT

**Note:** The following graduation project is available through Universidad San Francisco de Quito USFQ institutional repository. Nonetheless, this project – in whole or in part – should not be considered a publication. This statement follows the recommendations presented by the Committee on Publication Ethics COPE described by Barbour et al. (2017) Discussion document on best practice for issues around theses publishing available on <http://bit.ly/COPETheses>.

## RESUMEN

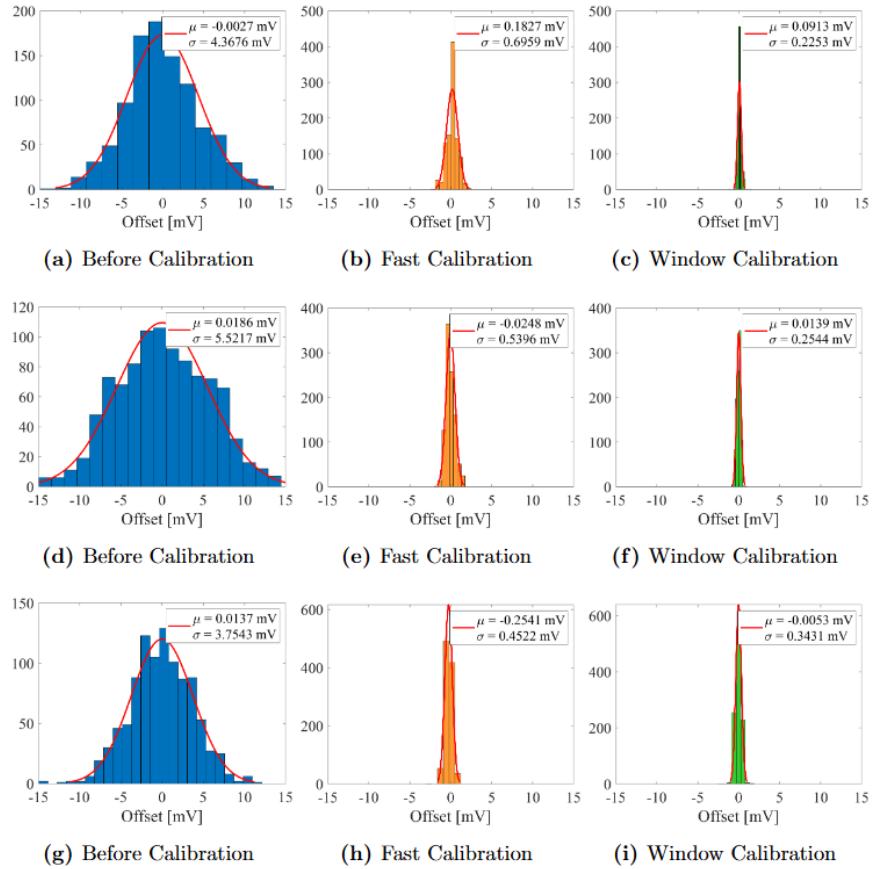

Este trabajo presenta el análisis y diseño de un comparador dinámico enfocado en la reducción del voltaje de offset. El comparador de dos etapas utiliza un amplificador inversor flotante en la primera etapa para minimizar la sensibilidad a las variaciones del voltaje de modo común de entrada ( $i\text{-}V_{cm}$ ). Las simulaciones mostraron un voltaje de offset de 3.18 mV y un nivel promedio de ruido de 699.80  $\mu\text{V}$  en diferentes valores de  $i\text{-}V_{cm}$ . Los análisis de energía y retardo revelaron trade-offs bajo variaciones de temperatura, voltaje de alimentación y esquinas de proceso. Las mediciones de los chips fabricados confirmaron cambios mínimos en los valores de offset y ruido con la variación de  $i\text{-}V_{cm}$ , demostrando baja sensibilidad. Debido a desajustes de fabricación, el voltaje de offset varió de -5.63 a 6.78 mV en 15 chips.

Se evaluaron una técnica de reducción de carga capacitiva y un método de calibración junto con otras dos técnicas: inyección de corriente mediante gate bias y a través de transistores en paralelo. Todas las técnicas se probaron bajo condiciones idénticas, centrándose en la precisión de salida, tiempo de calibración, consumo de energía, retardo e impacto en el área. El método de calibración propuesto mejoró el rendimiento de todas las técnicas, aunque con tiempos de calibración más largos. La técnica de carga capacitiva obtuvo los mejores resultados, logrando un offset de 1-sigma de 0.223 mV con el método de calibración propuesto.

Estos resultados confirman la efectividad de la técnica de reducción del voltaje de offset para mejorar la precisión y confiabilidad del comparador dinámico. Trabajos futuros podrían enfocarse en minimizar el ruido, optimizar el consumo de energía y reducir el retardo para mejorar la eficiencia general.

**Palabras clave:** Comparador dinámico, voltaje de offset, calibración, diseño CMOS, eficiencia energética.

## ABSTRACT

This work presents the analysis and design of a dynamic comparator focused on offset voltage reduction. The two-stage comparator employs a floating inverter amplifier in the first stage to minimize sensitivity to input common-mode voltage ( $i\text{-}V_{cm}$ ) variations. Simulations showed an offset voltage of 3.18 mV and an average noise level of 699.80  $\mu\text{V}$  across different  $i\text{-}V_{cm}$  values. Energy and delay analyses revealed trade-offs under temperature, supply voltage, and process corner variations. Measurements from fabricated chips confirmed minimal changes in offset and noise values with varying  $i\text{-}V_{cm}$ , demonstrating low sensitivity. Due to manufacturing mismatches, offset voltage ranged from -5.63 to 6.78 mV across 15 chips.

A capacitive load reduction technique and calibration method were evaluated alongside two other techniques: current injection by gate biasing and through parallel transistors. All techniques were tested under identical conditions, focusing on output accuracy, calibration time, energy, delay, and area. The proposed calibration method improved performance for all techniques, although with longer calibration times. The capacitive load technique achieved the best results, with a 1-sigma offset of 0.223 mV using the proposed calibration.

These results confirm the effectiveness of the offset reduction technique in improving comparator accuracy and reliability. Future work could focus on further minimizing noise, optimizing energy use, and reducing delay for enhanced efficiency.

**Key words:** Dynamic comparator, offset voltage, calibration, CMOS design, energy efficiency.

## TABLA DE CONTENIDO

|                                                                                 |           |

|---------------------------------------------------------------------------------|-----------|

| <b>Resumen .....</b>                                                            | <b>5</b>  |

| <b>Abstract .....</b>                                                           | <b>6</b>  |

| <b>Tabla de contenido .....</b>                                                 | <b>7</b>  |

| <b>ÍNDICE DE TABLAS .....</b>                                                   | <b>8</b>  |

| <b>ÍNDICE DE FIGURAS .....</b>                                                  | <b>9</b>  |

| <b>Introduction .....</b>                                                       | <b>10</b> |

| <b>Motivation.....</b>                                                          | <b>10</b> |

| <b>Overview of comparators .....</b>                                            | <b>12</b> |

| <b>Offset reduction techniques.....</b>                                         | <b>16</b> |

| <b>Design of the Two-Stage Comparator .....</b>                                 | <b>19</b> |

| <b>Pre-Amplifier Stage .....</b>                                                | <b>19</b> |

| <b>Latch Stage .....</b>                                                        | <b>22</b> |

| <b>Layout Design.....</b>                                                       | <b>23</b> |

| <b>Simulation and Analysis .....</b>                                            | <b>24</b> |

| <b>Simulation Setup .....</b>                                                   | <b>24</b> |

| <b>Offset Analysis.....</b>                                                     | <b>25</b> |

| <b>Input-Referred Noise Analysis.....</b>                                       | <b>27</b> |

| <b>Energy and Delay Analysis.....</b>                                           | <b>29</b> |

| <b>Variations in Temperature and Supply Voltage .....</b>                       | <b>30</b> |

| <b>Process Variation .....</b>                                                  | <b>33</b> |

| <b>Measurement of Fabricated Chips .....</b>                                    | <b>36</b> |

| <b>Measurement Setup .....</b>                                                  | <b>36</b> |

| <b>Noise and Offset Results .....</b>                                           | <b>37</b> |

| <b>Offset Reduction Techniques, Calibration, and Comparative Analysis .....</b> | <b>41</b> |

| <b>Selected Offset Reduction Techniques .....</b>                               | <b>41</b> |

| <b>Calibration Process .....</b>                                                | <b>50</b> |

| <b>Simulation Results and Comparison.....</b>                                   | <b>56</b> |

| <b>Conclusiones .....</b>                                                       | <b>62</b> |

| <b>Referencias .....</b>                                                        | <b>65</b> |

## ÍNDICE DE TABLAS

|                                                                      |    |

|----------------------------------------------------------------------|----|

| <b>Table 1:</b> Dynamic Comparators Characteristics Comparison ..... | 16 |

| <b>Table 2:</b> Offset Calibration Techniques .....                  | 18 |

| <b>Table 3:</b> Capacitors size and offset compensation step .....   | 42 |

| <b>Table 4:</b> Transistors size and offset compensation step .....  | 49 |

| <b>Table 5:</b> Calibration Methods Characteristics Comparison ..... | 61 |

## ÍNDICE DE FIGURAS

|                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 1:</b> StrongARM Latch (Razavi, 2015).....                                                                                                                            | 13 |

| <b>Figure 2:</b> Floating Inverter Amplifier .....                                                                                                                              | 19 |

| <b>Figure 3:</b> Floating Inverter Amplifier during the clock period .....                                                                                                      | 20 |

| <b>Figure 4:</b> Output Latch .....                                                                                                                                             | 22 |

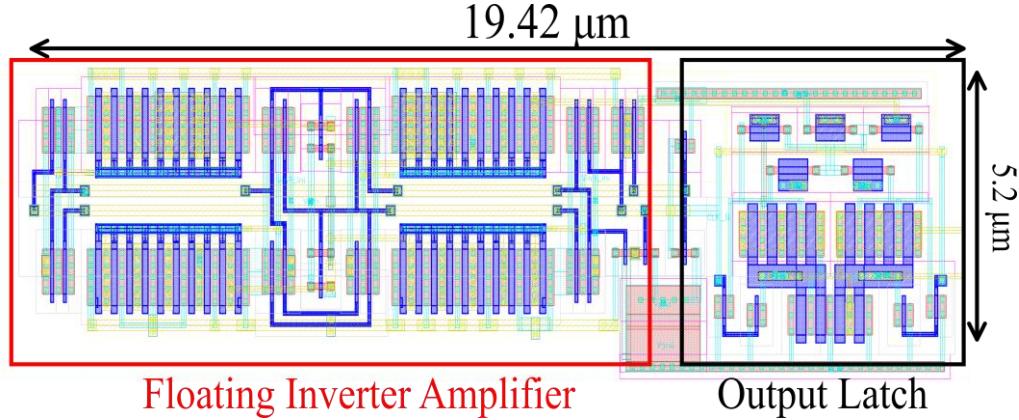

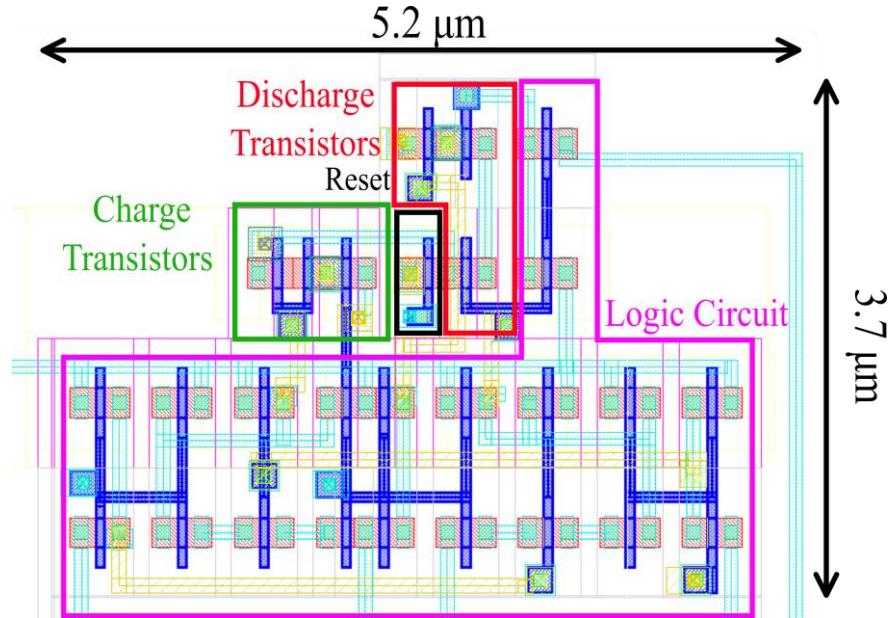

| <b>Figure 5:</b> Comparator Layout.....                                                                                                                                         | 24 |

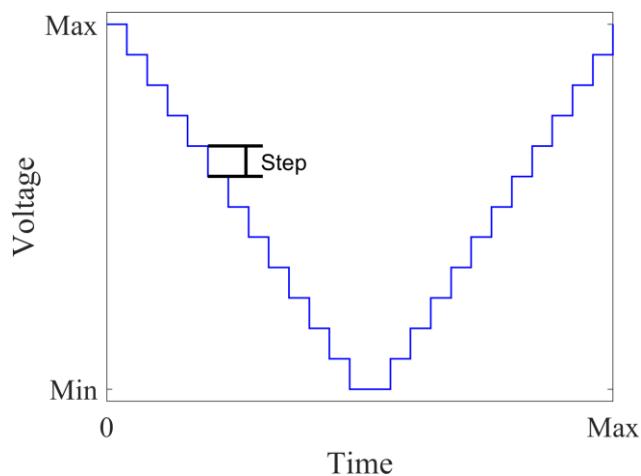

| <b>Figure 6:</b> Input Voltage Ramp.....                                                                                                                                        | 25 |

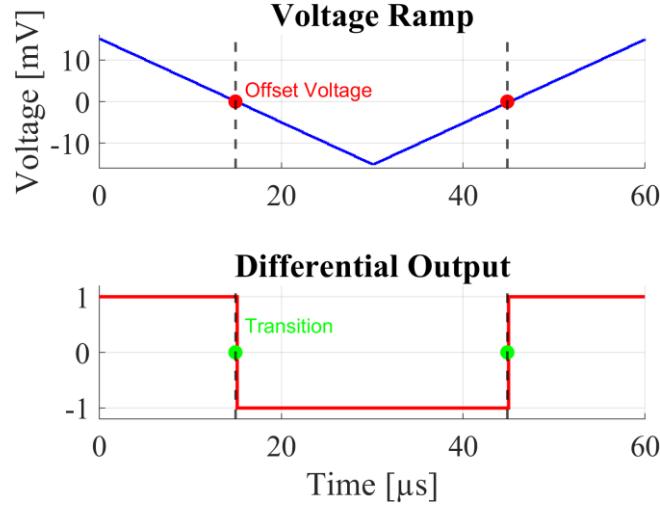

| <b>Figure 7:</b> Offset voltage measurement .....                                                                                                                               | 26 |

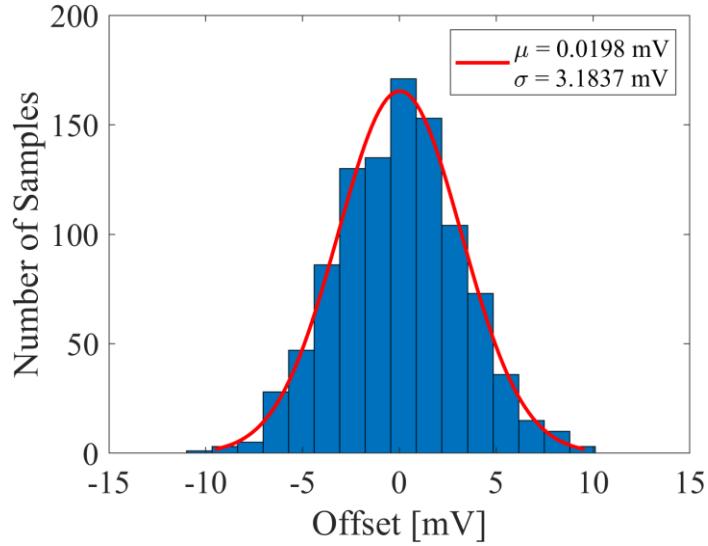

| <b>Figure 8:</b> Offset voltage normal distribution for $i\text{-}V_{cm}=600\text{ mV}$ .....                                                                                   | 27 |

| <b>Figure 9:</b> IRN at Input- $V_{cm}=600\text{ mV}$ .....                                                                                                                     | 28 |

| <b>Figure 10:</b> IRN at different Input- $V_{cm}$ .....                                                                                                                        | 29 |

| <b>Figure 11:</b> Energy and Delay in input common mode voltage variation .....                                                                                                 | 30 |

| <b>Figure 12:</b> Energy and Delay in Temperature Variation.....                                                                                                                | 31 |

| <b>Figure 13:</b> IRN in Temperature Variation.....                                                                                                                             | 31 |

| <b>Figure 14:</b> Energy and Delay in Supply Voltage Variation .....                                                                                                            | 32 |

| <b>Figure 15:</b> IRN in Supply Voltage Variation .....                                                                                                                         | 33 |

| <b>Figure 16:</b> Energy and Delay in Process Variation .....                                                                                                                   | 34 |

| <b>Figure 17:</b> IRN in Process Variation.....                                                                                                                                 | 35 |

| <b>Figure 18:</b> CDF for Chip 4 at $i\text{-}V_{cm} = 600\text{ mV}$ .....                                                                                                     | 36 |

| <b>Figure 19:</b> Measurement Setup .....                                                                                                                                       | 37 |

| <b>Figure 20:</b> Measured offset in chips for different $i\text{-}V_{cm}$ .....                                                                                                | 38 |

| <b>Figure 21:</b> Mean offset in chips for different $i\text{-}V_{cm}$ .....                                                                                                    | 38 |

| <b>Figure 22:</b> Measured noise in chips for different $i\text{-}V_{cm}$ .....                                                                                                 | 39 |

| <b>Figure 23:</b> Mean noise in chips for different $i\text{-}V_{cm}$ .....                                                                                                     | 40 |

| <b>Figure 24:</b> Capacitive Load added to the Latch Stage .....                                                                                                                | 41 |

| <b>Figure 25:</b> Layout Additional Capacitor Calibration Circuit .....                                                                                                         | 43 |

| <b>Figure 26:</b> Additional Transistors in the output stage for Charge Pump approach.....                                                                                      | 44 |

| <b>Figure 27:</b> Additional Components for the Gate Voltage Control for Charge Pump approach.                                                                                  |    |

| a) Charge Pump Circuit. b) Inputs and Outputs of the Charge Pump circuits .....                                                                                                 | 44 |

| <b>Figure 28:</b> Charging and Discharging of the Charge Pump .....                                                                                                             | 46 |

| <b>Figure 29:</b> Layout Additional Charge Pump Circuit.....                                                                                                                    | 47 |

| <b>Figure 30:</b> Parallel transistors added to the Latch Stage .....                                                                                                           | 48 |

| <b>Figure 31:</b> Layout Additional Parallel Transistors approach .....                                                                                                         | 50 |

| <b>Figure 32:</b> Noise Effect in the Comparator Output .....                                                                                                                   | 51 |

| <b>Figure 33:</b> Simulation Setup of the Comparator with the Calibration Block .....                                                                                           | 51 |

| <b>Figure 34:</b> Fast Calibration Method Flowchart .....                                                                                                                       | 52 |

| <b>Figure 35:</b> Fast Calibration Method Example .....                                                                                                                         | 53 |

| <b>Figure 36:</b> Window Calibration Method Flow Chart .....                                                                                                                    | 54 |

| <b>Figure 37:</b> Window Calibration Method Example .....                                                                                                                       | 55 |

| <b>Figure 38:</b> Offset calibration results. a), b), c) Capacitive Method. d), e), f) Current injection: Charge Pump. g), h), i) Current injection: Parallel Transistors ..... | 57 |

## INTRODUCTION

### **Motivation**

Comparators are essential building blocks in many electronic systems due to their ability to detect voltage differences and produce a digital output based on this difference. They are especially valuable in applications requiring quick decision-making, such as analog-to-digital converters (ADCs) (Hershberg, et al., 2021), where their fast response directly impacts overall system performance. ADCs rely on comparators to reduce the time needed to analyze signals by using the high-speed processing capabilities of the digital domain (Goll & Zimmermann, 2015).

These are widely used in technologies such as Ultra-Wideband (UWB) (Hung, Chang, & Lee, 2017), where they decode received signals before further processing in Digital Signal Processing (DSP) circuits. They also play an important role in Software-Defined Radio (SDR) (Sakr, Hussein, Fahmy, & Abdelghany, 2020), allowing ADCs and DACs (digital-to-analog converters) to be placed closer to the antenna, making system reconfiguration easier and more efficient. In these systems, the circuit compares an input signal (voltage, current, or charge) with a reference signal and outputs a digital logic state that indicates if the input is greater or smaller than the reference (Goll & Zimmermann, 2015).

In IoT sensors and wearable devices, as discussed in (Renteria-Pinon, Tang, & Tang, 2023), circuits select sampling points for real-time quantization. The processor predicts an upper and lower threshold for each sampling point, and a comparator checks if the input signal falls within these thresholds to determine if the prediction was accurate. This highlights the useful role of comparators in real-time signal processing.

Another application of dynamic comparators can be found in the design of a Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) for implantable biosensors

(Zhao, Li, Zhang, Liu, & Zhu, 2022; Shifman & Shor, 2024). In the design shown in (Zhao, Li, Zhang, Liu, & Zhu, 2022), a dynamic comparator with low offset and low kickback noise was used. The complete SAR ADC system includes two identical binary-weighted capacitive DACs, the dynamic comparator, SAR logic, a clock generator, and sampling switches. The low-offset comparator detects the differential voltage on the top plates of the capacitive DAC (CDAC) and sends the comparison results to the SAR logic block, enabling precise and efficient signal conversion.

In neuromorphic computing (Kim, et al., 2023; Rafiq, Chatterjee, Kumar, Singh Chauhan, & Sahay, 2024; Qi, y otros, 2023), where the circuit mimicks brain functions trying to reach a low-power consumption. One way to reduce power and area usage is by replacing high-precision ADCs, used in a previous neuromorphic circuit architecture, with a 1-bit dynamic comparator. In Spiking Neural Networks (SNNs), a type of neuromorphic network that models the behavior of biological neurons, output spikes (signals representing the firing of a neuron) are generated through a simple comparison between the neuron's membrane potential (represents the current state of the neuron) and a threshold, when this potential exceeds this threshold, the neuron fires and generates an output spike. Instead of using ADCs to detect this threshold crossing, dynamic comparators are employed resulting in lower power consumption and reduced area requirements (Kim, et al., 2023).

Some of the key factors to consider when designing CMOS dynamic comparators are ensuring an output accuracy, the ability to operate at low voltages, high speed, low power consumption, reliability, and minimal offset voltage (Sangeetha, et al., 2019).

## Overview of comparators

There are various types of comparators, each suited for different applications. Latched comparators, for example, exploit positive feedback to maintain an input-based decision once the comparator is triggered, ensuring stability in the output. Continuous comparators, on the other hand, constantly track the input signals, adjusting the output.

For high-speed applications, dynamic (or clock-regenerative) comparators are commonly used due to their rapid decision-making enabled by positive feedback. These comparators operate in two clocked phases: a precharge phase during the first clock half-cycle, which set specific nodes to either logic '0' or '1' depending on the latch design, and an evaluation phase that takes place during the second half-cycle, where the decision is made based on the input voltage difference. This dual-phase operation ensures that the comparator is ready to perform a decision on each clock cycle, making it ideal for high-speed signal processing (Goll & Zimmermann, 2015).

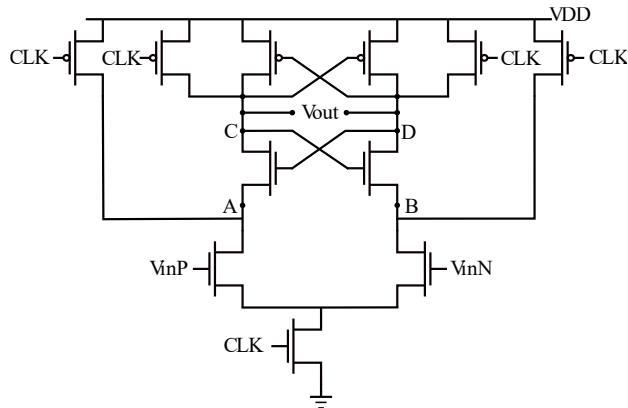

Structurally, dynamic comparators feature two main blocks: a differential input pair, which converts the input voltage difference into currents and can provide voltage gain, and a positive feedback latch to drive the final decision (Razavi, 2015). **Figure 1** shows the StrongARM Latch: during the precharge phase (CLK low), nodes A, B, C, and D are precharged to VDD. When CLK goes high, the differential input pair ( $V_{inP}$  and  $V_{inN}$ ) generates a current proportional to the differential input voltage, providing an initial amplification as the voltage difference  $V_A - V_B$  will grow exceeding the  $V_{inP} - V_{inN}$ . As nodes A and B discharge, NMOS transistors of the latch start to open the channel, allowing current flow at nodes C and D. This process triggers the PMOS transistors, creating the positive feedback that drives the final decision, forcing one output to Vdd and the other to zero (Razavi, 2015).

**Figure 1:** StrongARM Latch (Razavi, 2015)

In addition to the two main blocks, other critical component in dynamic comparators like the strong-arm latch are MOS switches responsible of pre-charging certain circuit nodes—critical for overall performance, either to VDD or GND depending on the design. Although a single NMOS or PMOS can generally handle this role, their on-resistance tends to vary significantly with input voltage. To address this issue, some designs use an NMOS and a PMOS connected in parallel, allowing the circuit to operate effectively across the entire voltage range while maintaining relatively low on-resistance.

Some key characteristics of a comparator are noise and offset. Noise introduces uncertainty in decision-making, with an increasing impact as the input voltage difference becomes close to zero. There are many types of noise sources, including supply voltage, ground noise, thermal noise, and kickback noise, that occurs during fast transitions at the output nodes, often due to positive feedback in the decision phase or resetting the output to a defined voltage.

Offset voltage is the differential input voltage required for switching from positive to negative or vice versa, the ideal offset voltage should be zero. However, this switching point may shift, resulting in a non-zero offset, caused by transistor mismatch at the fabrication process that yields variations of threshold voltage  $V_{th}$ , temperature gradients, or asymmetries in the design.

This effect can be minimized with a symmetrical layout and strategic circuit placement to reduce temperature effects from nearby circuitry (Goll & Zimmermann, 2015).

Additionally, noise and offset effects often interact in a comparator leading to incorrect decisions when the input signal is close to the offset voltage, as the noise may change the output in the wrong direction.

Designing and improving dynamic comparators has become essential as technology scales down, particularly due to their zero static power consumption (Krishna & Nambath, 2023). Key improvements focus on making comparators less sensitive to common-mode variation, as disturbances in real-world environments can shift the input levels and reduce decision accuracy. In (Tang, et al., 2020; Canal, Klimach, Bampi, & Balen, 2021), a floating inverter amplifier is used as the first stage, isolated with a floating reservoir capacitor to create virtual supply and ground rails. This design maintains a fixed common-mode voltage at the amplifier output, independent of the input common-mode, enhancing robustness against such variations.

Another key area of improvement is achieving high resolution in detecting small input voltage differences while minimizing delay. In (Krishna & Nambath, 2023), the comparator delay is reduced by using a cascode cross-coupled pair in the preamplifier, which increases gain by enhancing the output impedance through additional transistors. This approach improves delay across the input range, especially for small input differences and higher common-mode voltages, making it ideal for high-speed, high-resolution ADCs.

Reducing power consumption is also critical. In (Canal, Klimach, Bampi, & Balen, 2021), a comparator is designed to operate at low supply voltages by using a positive feedback bulk structure in the floating amplifier of the first stage. This structure reduces the threshold voltage dynamically, increasing transconductance and allowing higher gain and full operation

even with a reduced Vdd. This enables the comparator to operate with lower power consumption, ideal for high-performance and low-power applications.

Lastly, speed improvement is achieved in (Siddharth, Jaya Satyanarayana, Nithin Kumar, Vasantha, & Bonizzoni, 2020) by adding parallel discharge paths at the output, accelerating the discharge rate. This approach reduces delay by approximately 50% compared to a conventional Strong-Arm Latch comparator, enhancing speed without significant power consumption.

**Table 1** provides a quantitative comparison of these techniques. Works (Krishna & Nambath, 2023) and (Siddharth, Jaya Satyanarayana, Nithin Kumar, Vasantha, & Bonizzoni, 2020) show significantly lower delays (0.047\$ns\$ and 0.167\$ns\$): However, (Krishna & Nambath, 2023) has a drawback with a higher offset voltage (11.38 \$mV\$) and noise (750 \$\mu\$V\$), which can affect precision, while (Siddharth, Jaya Satyanarayana, Nithin Kumar, Vasantha, & Bonizzoni, 2020) shows a lower offset, indicating its advantage in high-accuracy applications.

|                     | (Tang, et al., 2020) | (Krishna & Nambath, 2023) | (Canal, Klimach, Bampi, & Balen, 2021) | (Siddharth, Jaya Satyanarayana, Nithin Kumar, Vasantha, & Bonizzoni, 2020) |

|---------------------|----------------------|---------------------------|----------------------------------------|----------------------------------------------------------------------------|

| Process [nm]        | 180                  | 65                        | 28                                     | 65                                                                         |

| Supply voltage [V]  | 1.2                  | 1.1                       | 0.6                                    | 1                                                                          |

| Offset Voltage [mV] | -                    | 11.38                     | 5                                      | 2.05                                                                       |

| Noise [\$\mu\$V]    | 46                   | 750                       | 237                                    | -                                                                          |

|             |      |       |       |       |

|-------------|------|-------|-------|-------|

| Energy [pJ] | 0.98 | 0.081 | 0.038 | 0.108 |

| Delay [ns]  | 11   | 0.047 | 5.77  | 0.167 |

**Table 1:** Dynamic Comparators Characteristics Comparison

(Canal, Klimach, Bampi, & Balen, 2021) achieves the lowest energy consumption (0.038 pJ) with a 0.6 V supply, optimized for low-power design. For precision, (Siddharth, Jaya Satyanarayana, Nithin Kumar, Vasantha, & Bonizzoni, 2020) and (Tang, et al., 2020) have the lowest offset voltage (2.05 mV) and noise (46  $\mu$ V), respectively, making them suitable for noise-sensitive, high-accuracy applications. These are some of the trade-offs between speed, power efficiency, and accuracy, addressing key requirements for high-performance comparator designs, with (Siddharth, Jaya Satyanarayana, Nithin Kumar, Vasantha, & Bonizzoni, 2020) standing out as a balanced option for speed, power consumption, and precision.

### Offset reduction techniques

The offset in comparators primarily results from mismatches between the transistors on both sides of the circuit, which ideally should be symmetric but often are not. The transistors that have the most significant impact on the offset are those that are activated first, as opposed to those that are turned on later in the process (Razavi, 2015).

This is a critical limitation, as it can lead to errors in detecting small signals. Several techniques have been developed to reduce offset. One such method is static offset cancellation, which involves adding extra transistors or other components to provide additional load capacitance or current on the unbalanced side. Another approach is dynamic offset cancellation, which incorporates an additional stage before the comparator, that senses the offset and attempts to correct it to prevent it from affecting the latch stage. However, it is important to note that the latch can also contribute to the offset. Therefore, it is possible to apply both

techniques within the same comparator to minimize the overall offset (Goll & Zimmermann, 2015).

Several studies have proposed techniques to reduce offset. For example, as seen in (Tsirmpas, Kontelis, Souliotis, & Plessas, 2024; Jaiswal, et al., 2020; Lee, et al., 2020; Sharma, Srivastava, Hande, Sehgal, & Das, 2023; Ahrar & Yavari, 2021), some approaches control the current flowing to the latch from the output of the first stage. In (Tsirmpas, Kontelis, Souliotis, & Plessas, 2024; Lee, et al., 2020; Sharma, Srivastava, Hande, Sehgal, & Das, 2023; Ahrar & Yavari, 2021), parallel transistors are sequentially activated based on the offset magnitude. In (Jaiswal, et al., 2020), a charge pump is used to provide voltage to two additional transistors, one on each side of the first stage output, to increase or decrease current. In (Ahrar & Yavari, 2021; Yousefirad & Yavari, 2021), body bias control is applied to the differential input pair transistors, adjusting their threshold voltage  $V_{th}$  according to the offset.

These methods require sensing the comparator outputs to determine the direction of mismatch and activate its calibration mechanism. As a result, digital control is necessary for effective calibration. **Table 2** shows the calibration techniques used in the referenced works, along with the initial offset values, the calibrated offsets achieved, and their consumed energy.

|              | (Tsirmpas, Kontelis, Souliotis, & Plessas, 2024) | (Jaiswal, et al., 2020) | (Lee, et al., 2020) | (Sharma, Srivastava, Hande, Sehgal, & Das, 2023) | (Ahrar & Yavari, 2021) | (Yousefirad & Yavari, 2021) |

|--------------|--------------------------------------------------|-------------------------|---------------------|--------------------------------------------------|------------------------|-----------------------------|

| Process [nm] | 65                                               | 180                     | 14                  | 180                                              | 180                    | 180                         |

|                        |                   |                   |                   |                   |                               |           |

|------------------------|-------------------|-------------------|-------------------|-------------------|-------------------------------|-----------|

| Supply Voltage [V]     | 1                 | 1.8               | 0.9               | 1.8               | 1                             | 1         |

| Calibration Technique  | Discharge Current - Body Bias | Body Bias |

| Initial Offset [mV]    | 16                | 2.72              | 2.073             | 2.85              | 19.56                         | 13.2      |

| Calibrated Offset [mV] | 1                 | 0.013             | 0.259             | 0.445             | 0.363                         | 0.3       |

| Energy [pJ]            | -                 | 0.134             | 0.214             | 0.155             | 0.952 – 10.66                 | 0.036     |

**Table 2:** Offset Calibration Techniques

The main objective of this work is to design and characterize a dynamic comparator. This involves analyzing its performance concerning energy consumption, noise, and delay across different input common modes, supply voltages, and temperature variations, as well as different process corners. After that, a compensation method will be introduced to reduce the offset voltage. The rest of the thesis is organized as follows. Chapter “Design of the Two-Stage Comparator” details the design of the two-stage comparator, including the pre-amplifier stage, output latch and layout. Chapter “Simulation and Analysis” focuses on the implementation of the simulations and their results. Chapter “Measurement of Fabricated Chips” presents the measurement setup and the results obtained from 15 fabricated chips, including noise and offset voltage. Finally, Chapter “Offset Reduction Techniques, Calibration, and Comparative

Analysis” introduces the offset reduction techniques, calibration process and a comparative analysis of the simulation results.

## DESIGN OF THE TWO-STAGE COMPARATOR

### Pre-Amplifier Stage

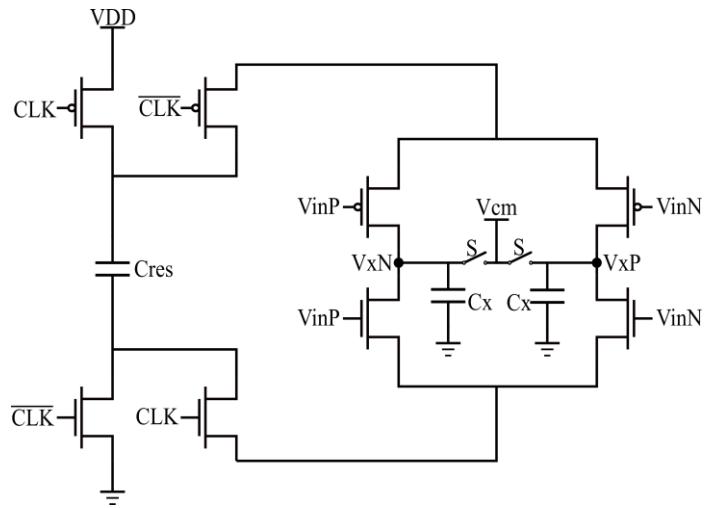

The first stage of the comparator is a pre-amplifier for the differential input signal ( $V_{inP}$  and  $V_{inN}$ ) that reports the input voltages to a level that the latch can reliably detect. The Floating Inverter Amplifier (FIA) showed in **Figure 2** used in (Tang, et al., 2020; Canal, Klimach, Bampi, & Balen, 2021) is designed to enhance the performance of dynamic comparators, this block introduces combines pre-amplification with improvements in energy efficiency and noise management.

**Figure 2:** Floating Inverter Amplifier

The architecture integrates a floating reservoir capacitor,  $C_{res}$ , which enhances the stability of the dynamic comparator against variations in process corners and fluctuations in input common-mode voltage. By merging two conventional head and tail capacitors into a single floating reservoir capacitor, this design achieves a significant 75% reduction in total

capacitance (Tang, et al., 2020) showing that this design better adapts to variations in the circuit's operating conditions.

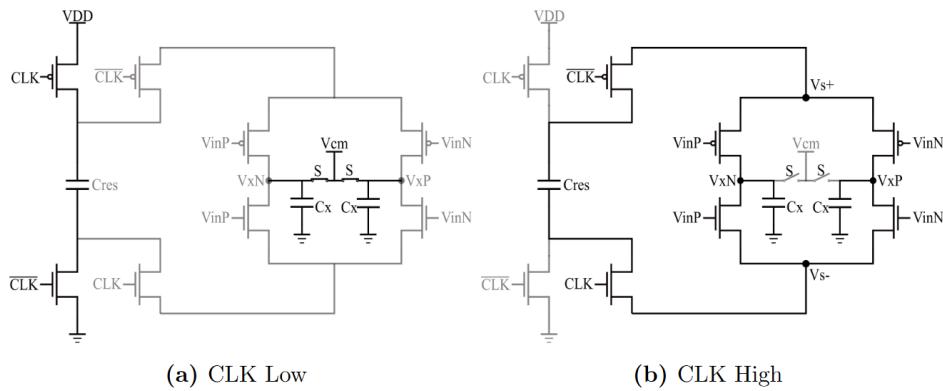

The capacitor  $C_{res}$  is connected through MOS switches controlled by the clock signal. During the low phase of the clock, the capacitor is connected to  $V_{DD}$  and ground (**Figure 3a**), allowing it to recharge and maintain a stable reference level. In the high phase, the capacitor connects to the FIA, enabling operation within an isolated voltage domain, as shown in **Figure 3b**. This configuration helps maintain a consistent output common-mode voltage, essential for minimizing the impact of voltage fluctuations in the following stage.

**Figure 3:** Floating Inverter Amplifier during the clock period

Additionally, this architecture balances the input and output currents of the reservoir capacitor. When the input voltages are equal, such as in a common-mode condition, the design forces the common-mode current entering the integration capacitor ( $C_x$ ) to zero. This ensures that the output common-mode voltage remains stable without requiring an additional circuit for common-mode feedback.

As explained in (Tang, et al., 2020), this FIA is designed to work in a low-power mode because its transistors operate near the subthreshold region. This means that as the gate-source

voltage  $V_{gs}$  decreases, the transistors stay in this low-power region, which significantly reduces energy consumption.

To analyze the gain of the amplifier in this low-power mode, we first study its transconductance,  $Gm$  in the subthreshold region. The transconductance describes the relationship between the input voltage and the resulting current. In this region,  $Gm$  is calculated based on the amplifier's tail current  $I_{amp}$  divided by the thermal voltage  $U_T$  and the factor  $n$  that depends on the transistor characteristics. The equation ( 10 ) shows that in the subthreshold region, the transconductance mainly depends on the tail current:

$$Gm(t) \cong \frac{I_{amp}}{n \cdot U_T} \quad (1)$$

Next, the differential output voltage of the amplifier,  $\Delta V_{X,DM}$  depends on the differential input voltage and the transconductance over time. The output voltage can be determined by integrating the previously mentioned factors:

$$\Delta V_{X,DM}(t) = \frac{\int_0^t \Delta V_{I,DM} \cdot G_m(\tau) d\tau}{Cx} \simeq \frac{\Delta V_{I,DM} \int_0^t I_{amp}(\tau) d\tau}{n \cdot U_T \cdot Cx} \quad (2)$$

The equation ( 2 ) shows that the differential output voltage  $\Delta V_{X,DM}$  is influenced by the variation of the tail current over time.

The variation in the source nodes of the PMOS and NMOS transistors ( $V_{s+}$  and  $V_{s-}$ ) over time, is defined in equation ( 3 ), where  $\Delta V_S$  is also affected by the tail current and the reservoir capacitance  $C_{res}$ .

$$\Delta V_S(t) = \frac{\int_0^t I_{amp}(\tau) d\tau}{2 \cdot C_{res}} \quad (3)$$

Finally, to obtain the amplifier's gain during the comparison time  $T_{int}$ , it is been used the equation ( 4 ) .

$$A_V = \frac{\Delta V_{X,DM}(T_{int})}{\Delta V_{I,DM}} = \frac{2 \cdot C_{res} \cdot \Delta V_s(T_{int})}{n \cdot C_x \cdot U_T} \quad ( 4 )$$

This expression shows that the gain mainly depends on the change in source voltage  $\Delta V_s$  , which is determined by how the tail current varies over time. This approach ensures that the amplifier achieves a high gain, even while operating in a low-power mode.

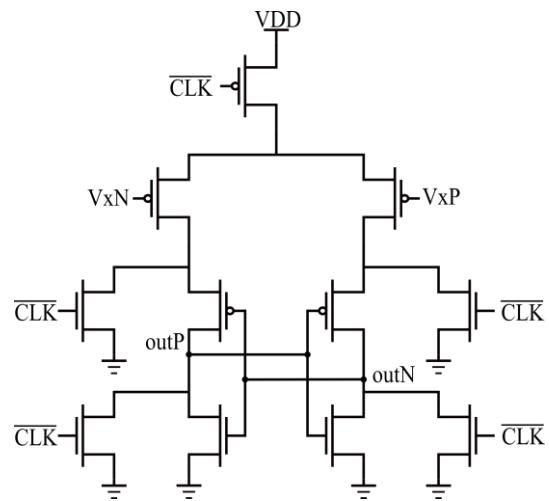

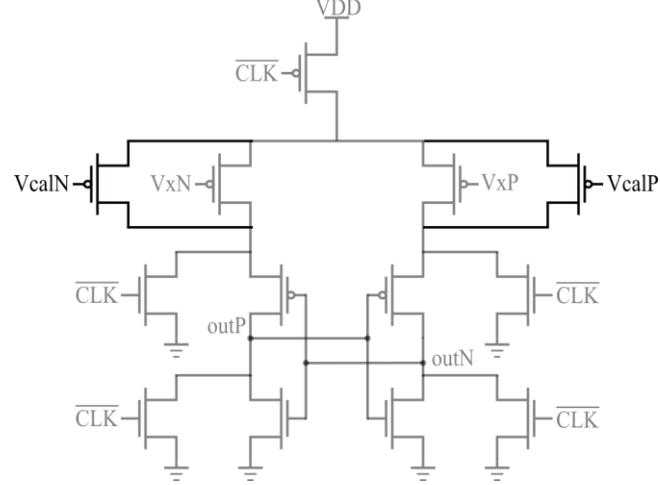

### Latch Stage

The second stage is a clocked latch, illustrated in **Figure 4**, responsible for generating a digital output based on the amplified differential input from the previous stage. It receives the pre-amplifier output signals,  $V_{xN}$  and  $V_{xP}$ . During the low phase of the clock, these nodes are grounded, which resets the latch and prepares it for the next evaluation cycle. In the high phase, the latch is connected to  $VDD$ , and it starts the decision process according to the input differential signals.

**Figure 4:** Output Latch

This operates similarly to the StrongArm Latch but with the main modification of the addition of the previous stage, so the input signals in this latch are designed to be insensitive to changes in the input common-mode voltage, this insensitivity improves the reliability of the digital output, as it reduces the effects of input voltage variations.

The comparator's differential output, noted as  $\Delta Out$ , is obtained by taking the difference (equation ( 5 )) between the two latch outputs: OutP and OutN. Since the output latch signal is taken as digital,  $\Delta Out$  can be represented as either 1 or -1, as shown in equation ( 6 ). When OutP is high and OutN is low,  $\Delta Out$  is 1. On the other hand, when OutP is low and OutN is high,  $\Delta Out$  becomes -1.

$$\Delta Out = OutP - OutN \quad (5)$$

$$\Delta Out = \begin{cases} 1 & \text{if } OutP = 1 \text{ and } OutN = 0 \\ -1 & \text{if } OutP = 0 \text{ and } OutN = 1 \end{cases} \quad (6)$$

## Layout Design

The layout of the complete comparator, shown in **Figure 5**, was created to estimate the occupied area and enable post-layout simulations for more accurate analysis of its performance characteristics. As observed, the FIA occupies more than half of the total area, which is 100.98  $\mu m^2$ .

**Figure 5:** Comparator Layout

## SIMULATION AND ANALYSIS

### Simulation Setup

The simulation of the two-stage comparator was performed using Cadence Virtuoso in a 65nm commercial technology, focusing on offset, noise, energy consumption, and delay. The setup included configuring the circuit for analysis in nominal conditions with a supply voltage of 1.2 V, a temperature of 27 °C, and following simulations under changes across process variation to characterize the comparator's behavior under different fabrication conditions. Finally, simulations across a range of temperatures and supply voltages to examine their effects on performance.

To assess sensitivity, the input common-mode voltage ( $i\text{-}V_{\text{cm}}$ ) was adjusted, while a sweep of the differential input voltage ( $\Delta V_{\text{in}}$ ) was used to evaluate both power consumption and delay. Additionally, noise analysis was conducted by enabling transient noise in the simulation, allowing for an evaluation of its impact on the comparator's decision accuracy.

## Offset Analysis

To evaluate the offset, a Monte Carlo simulation was conducted, which is convenient for analyzing the effects of random variations, such as mismatches due to the manufacturing process. These random mismatches lead to differences in device characteristics, the Monte Carlo simulation is an effective method to statistically analyze the offset by examining multiple instances of the circuit.

For this analysis, it was applied the methodology described in \cite{offset\_meth}, where a differential input voltage ramp, shown in **Figure 6**, is used. This ramp, generated with Verilog-A code, sweeps from the minimum value of  $-15 \text{ mV}$  to a maximum of  $15 \text{ mV}$  with a step size of  $0.2 \text{ mV}$ , this differential voltage will be centered around a  $i\text{-}V_{cm}$  at the comparator inputs. By applying this ramp, we can track the necessary input level for the comparator output to change its logic state. In an ideal scenario, the transition would occur at zero differential input; however, due to manufacturing mismatches, this switching occurs at a nonzero differential input, showing the offset voltage.

**Figure 6:** Input Voltage Ramp

The offset voltage is determined by finding the  $\Delta V_{in}$  at which the differential output transitions from  $-1$  to  $1$  (or vice versa). This measurement is taken for both the rising and falling

parts of the ramp to obtain an average offset value, an example is shown in **Figure 7** where the offset is given ideally at 0 mV in the ramp during the transitions.

**Figure 7:** Offset voltage measurement

After completing 1000 Monte Carlo simulation runs, the offset voltage results in a normal distribution, where the mean is expected to be close to zero, and the standard deviation reflects the spread caused by process variations. **Figure 8** shows this distribution when the  $V_{cm}$  is set to 600 mV. The offset values follow the normal distribution centered around a mean ( $\mu$ ) of 0.0198 mV, showing that on average, the comparator offset is very close to zero, as expected. The standard deviation ( $\sigma$ ) shows a spread of 3.184 mV out from the mean, suggesting that most offset values lie within  $\pm 3$  mV of the mean, the distribution gives useful information about the offset performance of the comparator, as a low mean and moderate standard deviation indicate that the comparator offset is generally small across the Monte Carlo simulation.

**Figure 8:** Offset voltage normal distribution for  $i\text{-}V_{cm}=600\text{ mV}$

### Input-Referred Noise Analysis

Input-Referred Noise (IRN) analysis is essential for assessing how noise influences the comparator's accuracy and stability. Transient noise was used, the noise factor was incrementally adjusted until the simulated noise produced an IRN value comparable to the measurements obtained from the fabricated chip. This process ensured that the noise levels in the simulation matched the real-world conditions, providing a precise representation of how the design would behave in actual noisy situations.

It was characterized by conducting 1000 measurements at each  $\Delta V_{in}$  step, sweeping from  $-7\text{ mV}$  to  $7\text{ mV}$  in increments of  $0.2\text{ mV}$ , this allows us to determine the probability of obtaining specific output values at each  $\Delta V_{in}$  step. The number of 1's obtained was counted at the  $\Delta V_{out}$ , observing that as  $\Delta V_{in}$  increased, the occurrence of 1's also increased, then, the probability was calculated by dividing the obtained number of 1's by the total measurements (1000 in this case). The obtained curve was used to calculate the standard deviation of the output distribution, which shows the noise impact on the comparator.

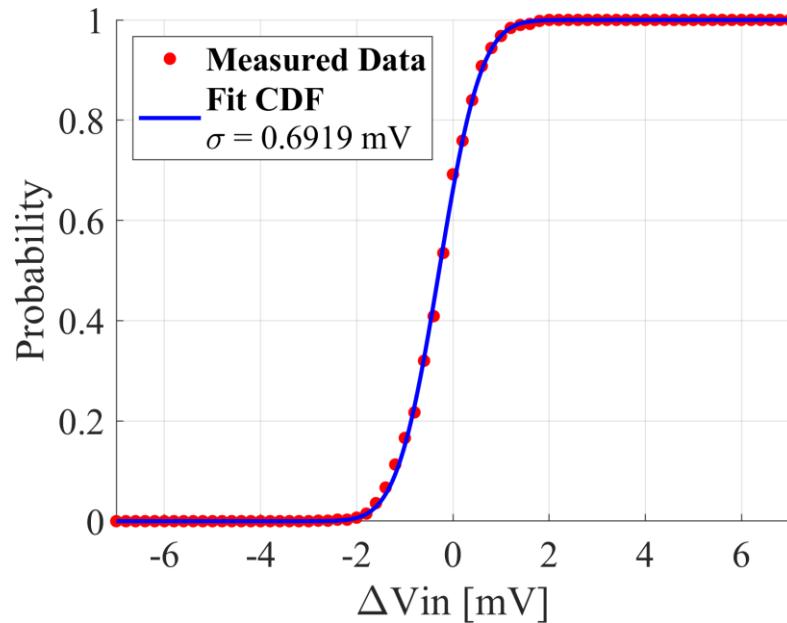

For the interpretation of these values, the output data was fit to a Cumulative Distribution Function (CDF). This CDF fitting provides a visual representation of the noise effect by showing the probability trend across  $\Delta V_{in}$  values, as shown in **Figure 9** for common-mode input voltage of 600 mV, the IRN is 0.692 mV. This shows how noise affects the comparator's switching during the variation of the  $\Delta V_{in}$ .

**Figure 9:** IRN at Input-Vcm=600 mV

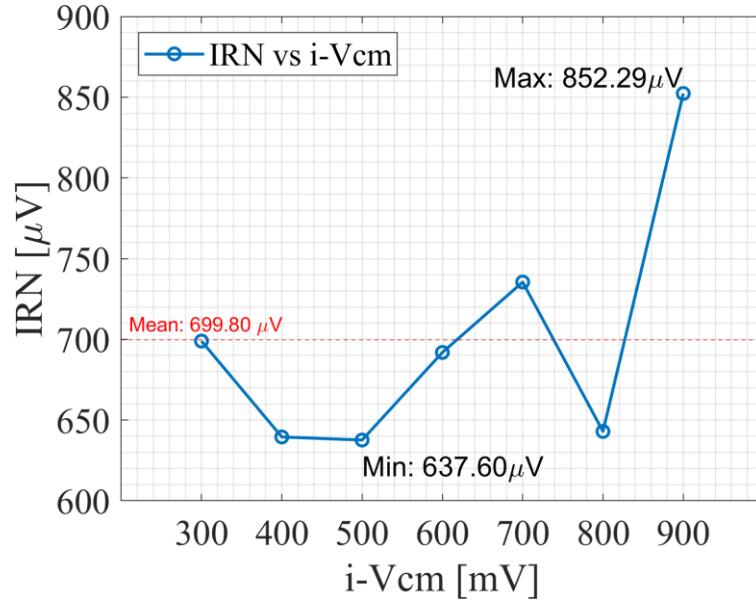

The IRN versus i-Vcm plot shown in **Figure 10** provides the noise performance of the comparator across different input conditions, it has a mean value of approximately 699.80  $\mu$ V, with minimum and maximum values of 637.60  $\mu$ V and 852.29  $\mu$ V, respectively. Also, it remains fairly consistent between 300 mV and 800 mV i-Vcm, suggesting that the comparator maintains a consistent noise performance within this range. However, as i-Vcm approaches 900 mV, there is a sharp increase in IRN, which may indicate an increased sensitivity to common-mode variations at higher input levels. This trend suggests that the comparator may work better for applications where the i-Vcm remains within that stable range, as performance gets worse at the extreme.

**Figure 10:** IRN at different Input-Vcm

### Energy and Delay Analysis

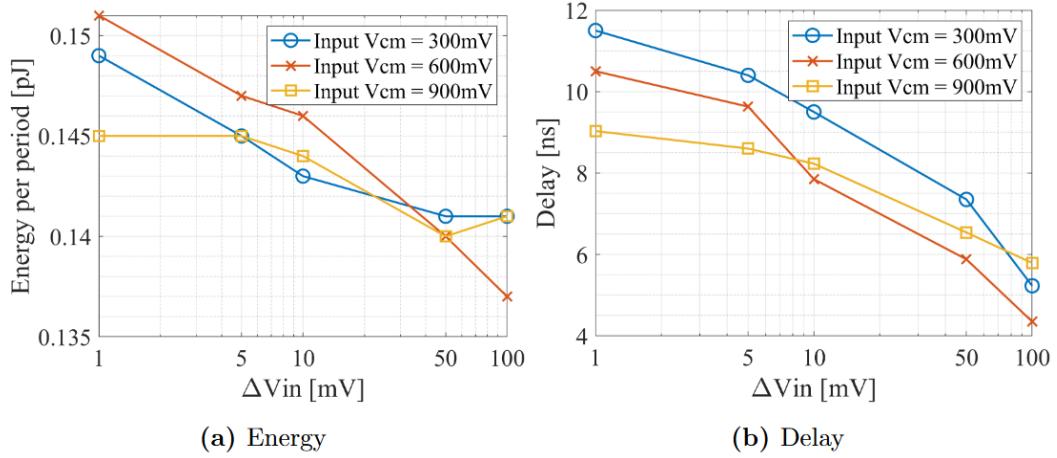

Energy consumption and delay are two key metrics that impact the efficiency of the comparator. This analysis looks at how energy and delay change with different input conditions, including the i-Vcm and variations in  $\Delta Vin$ . Simulations were performed for three i-Vcm levels (300 mV, 600 mV, and 900 mV) with  $\Delta Vin$  values of 1, 5, 10, 50, and 100 mV for each.

As shown in **Figure 11**,  $\Delta Vin$  has a clear effect: when  $\Delta Vin$  is smaller, the comparator needs more energy and time to make a decision, which increases both energy consumption and delay. For i-Vcm variation, the maximum difference in energy is 0.006 pJ, which is quite small, indicating that FIA keeps the comparator stable against changes in i-Vcm. Similarly, i-Vcm has only a small effect on delay.

**Figure 11:** Energy and Delay in input common mode voltage variation

### Variations in Temperature and Supply Voltage

The performance of the comparator was analyzed under varying temperature and supply voltage conditions to assess its robustness.

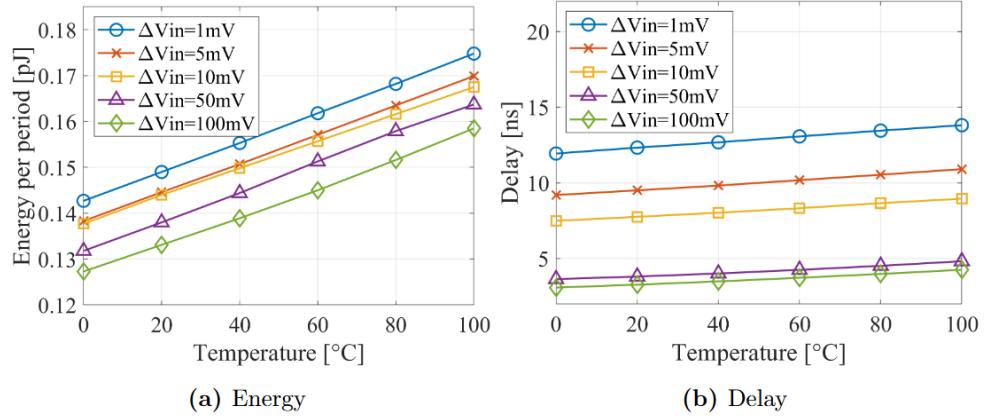

**Figure 12** shows how energy consumption and delay change with temperature for different  $\Delta V_{in}$  in the comparator. In **Figure 12a**, energy consumption increases noticeably with increasing temperature, regardless of the  $\Delta V_{in}$  value. The increase in energy from  $0\text{ }^{\circ}\text{C}$  to  $100\text{ }^{\circ}\text{C}$  is approximately  $0.032\text{ pJ}$ , which is translated to about  $0.0064\text{ pJ}$  per  $20\text{ }^{\circ}\text{C}$ . This trend shows that the comparator becomes less energy-efficient at higher temperatures. In contrast, **Figure 12b** shows that delay remains relatively stable across the analyzed temperature range, with only a minor variation of around  $1\text{ ns}$  between the lowest and highest temperatures. Overall, the results suggest that it mainly affects energy consumption rather than delay, with higher temperatures leading to increased energy use while delay remains mostly unchanged.

**Figure 12:** Energy and Delay in Temperature Variation

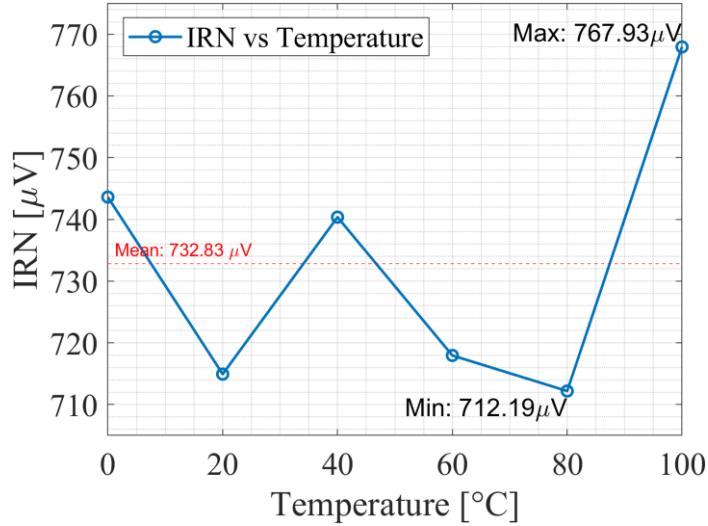

**Figure 13** shows how IRN changes with temperature. As we can see, the IRN varies significantly across the temperature range of 0 °C to 100 °C. The noise level reaches its lowest value, 712.19  $\mu V$ , at around 80 °C, while the highest noise level, 767.93  $\mu V$ , occurs at 100 °C. The mean IRN across all temperatures is 732.83  $\mu V$ , indicated by the red dashed line.

**Figure 13:** IRN in Temperature Variation

These results suggest that temperature does not have a big impact on the noise levels as opposed to i-Vcm variations, with IRN increasing notably at higher temperatures. Such variations in noise can affect the accuracy and stability of the circuit's performance.

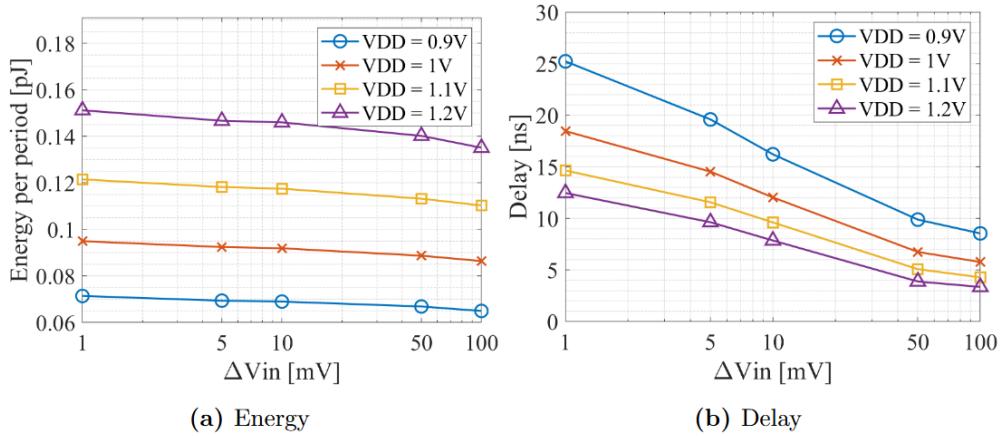

**Figure 14** shows how energy consumption per period and delay vary with changes in VDD and  $\Delta Vin$ . In **Figure 14a**, can be observed that energy usage decreases slightly as  $\Delta Vin$  increases across all supply voltages. The lowest energy consumption occurs at VDD = 0.9 V, while the highest is at VDD = 1.2 V, indicating that higher supply voltages result in greater energy usage. The difference between the lowest and highest energy consumption is approximately 0.08 pJ and remains nearly constant across all  $\Delta Vin$  values. This shows that variations in supply voltage have a more significant impact on energy consumption than changes in  $\Delta Vin$ . In **Figure 14b**, the delay also decreases as  $\Delta Vin$  increases. The delay meets its maximum at VDD = 0.9 V and the minimum at VDD = 1.2 V, with a difference of 13 ns at  $\Delta Vin$  = 1 mV, while at  $\Delta Vin$  = 100 mV the difference gets reduced to 5 ns . This shows that a higher supply voltage reduces delay, making the circuit behave faster, but its impact gets reduced as the  $\Delta Vin$  increases, different from energy analysis, where supply voltage consistently affects energy consumption across all the  $\Delta Vin$  values.

**Figure 14:** Energy and Delay in Supply Voltage Variation

Increasing the supply voltage leads to higher energy consumption but reduces delay, these trade-offs have to be analyzed based on the performance and power efficiency requirements.

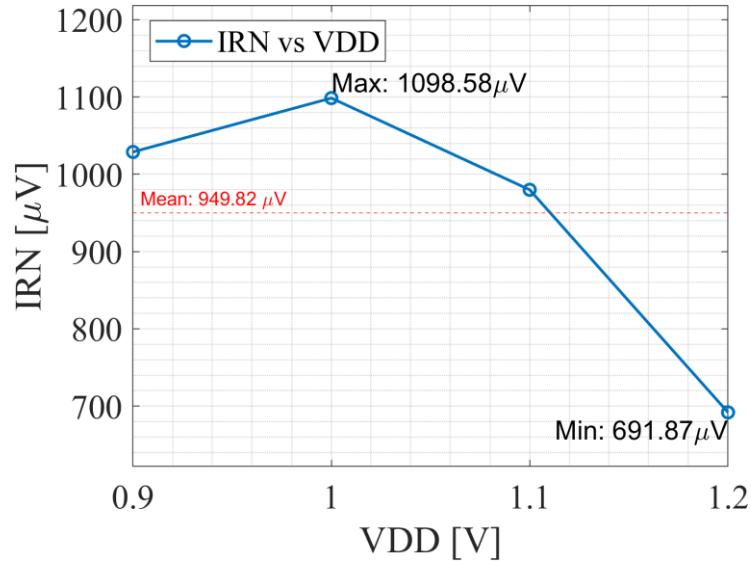

**Figure 15** shows the variation of IRN with different VDD. The plot shows that IRN decreases as VDD increases from 1 V to 1.2 V. The highest noise level,  $1098.58 \mu V$ , occurs at  $VDD = 1 V$ , while the lowest noise of  $691.87 \mu V$ , is observed at  $VDD = 1.2 V$ . The mean IRN across all supply voltages is  $949.82 \mu V$ , which shows that the VDD highly affects noise performance.

**Figure 15:** IRN in Supply Voltage Variation

These results highlight the impact of supply voltage on noise levels. Higher supply voltages result in lower IRN, which could improve the precision and stability of the circuit. Therefore, in the need for a low-power application, noise will be affected by reducing the VDD.

## Process Variation

To evaluate the impact of process variations, simulations were performed for different process corners: TT (Typical-Typical), SS (Slow-Slow), SF (Slow-Fast), FS (Fast-Slow) and FF(Fast-Fast).

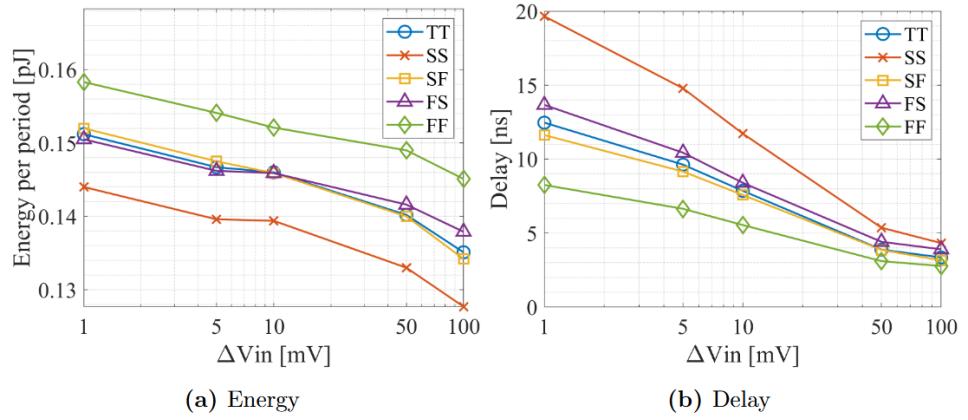

**Figure 16** shows the effects of process variation on both energy consumption and delay as the input voltage difference increases.

**Figure 16:** Energy and Delay in Process Variation

In **Figure 16a**, we see that energy consumption decreases as  $\Delta Vin$  increases across all corners. However, the FF corner has higher energy consumption, approximately 0.014 pJ more than the SS corner in each  $\Delta Vin$  variation. This pattern shows that process variations can result in notable differences in energy usage, which could be critical for power-sensitive applications. Delay also is diminished as  $\Delta Vin$  increases in **Figure 16b**, with SS showing the longest delay and FF the shortest. In general, corners with lower energy consumption, such as SS, tend to have longer delays, while those with higher energy usage, such as FF, exhibit shorter delays. At  $\Delta Vin = 1$  mV, the impact of process variation on delay is most noticeable, with a difference of 11 ns between the SS and FF corners. However, this difference gradually decreases as  $\Delta Vin$  increases, reducing to about 3 ns at  $\Delta Vin = 100$  mV. This correlation shows that circuits operating in processes that make the circuits consume more energy may also perform faster.

Thus, the difference in energy and delay across the corners highlights the importance of considering process variation when designing for consistent speed, given that delays and energy consumption can change considerably depending on the specific process.

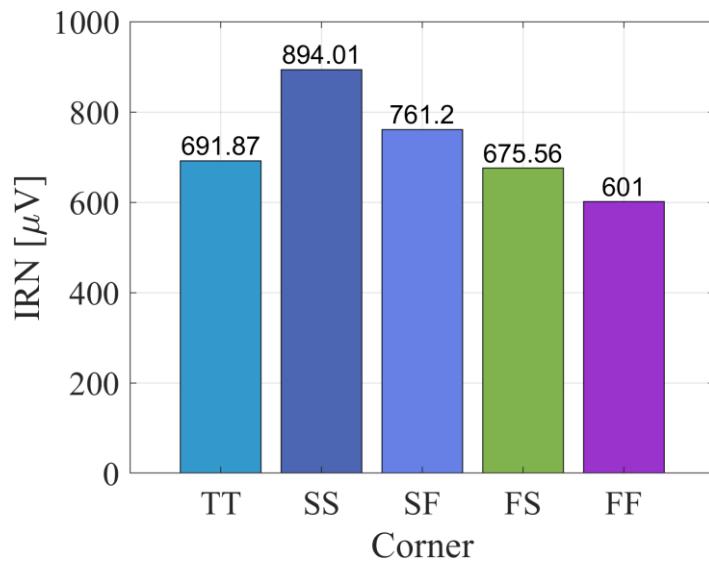

**Figure 17** shows the IRN across different process corners. The SS corner has the highest IRN with  $894.01 \mu V$ , showing that it is more sensitive to noise, while the FF corner has the lowest at  $601 \mu V$ . Comparing this with the energy and delay results, circuits in the SS corner consume less energy but experience higher noise levels and longer delays. On the other hand, the FF corner has lower noise and shorter delays but consumes more energy. This comparison points out how process variations impact performance and energy efficiency, with each corner exhibiting trade-offs between noise sensitivity, delay, and power consumption.

**Figure 17:** IRN in Process Variation

## MEASUREMENT OF FABRICATED CHIPS

### Measurement Setup

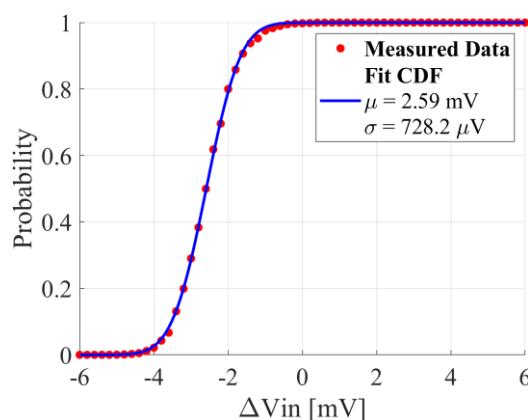

The comparator analyzed in **Chapter “Design of the Two-Stage Comparator”** and with simulation results shown in **Chapter “Simulation and Analysis”** was fabricated. Fifteen chips were tested using a supply voltage of  $1.2\text{ V}$  and a common-mode voltage of  $0.6\text{ V}$ . The comparator inputs ( $V_{inP}$  and  $V_{inN}$ ) were set to a differential input  $\Delta V_{in} = V_{inP} - V_{inN}$  from  $-6\text{ mV}$  to  $6\text{ mV}$ , with steps of  $0.2\text{ mV}$ . If the offset voltage fell outside this range, the window was adjusted to ensure accurate measurement. This setup was tested at input common-mode voltages of  $300\text{ mV}$ ,  $400\text{ mV}$ ,  $500\text{ mV}$ , and  $600\text{ mV}$ . For each  $\Delta V_{in}$  step, an FPGA was configured to take 3000 measurements of the comparator outputs to determine the probability of obtaining a "1" in all the samples. This process was repeated 10 times for each step to obtain an average for each measurement, this process is similar to the one performed with the IRN in the simulation. After obtaining the average probability of 1's for each step, the data was fitted to a CDF, where the mean ( $\mu$ ), represents the offset of the comparator, and the standard deviation ( $\sigma$ ), represents the IRN. An example of the measured data for one chip with an input common-mode voltage of  $600\text{ mV}$  is shown in **Figure 18**, where the offset voltage is  $2.59\text{ mV}$  and the IRN is  $728.2\mu\text{V}$ .

**Figure 18:** CDF for Chip 4 at  $i\text{-}V_{cm} = 600\text{ mV}$

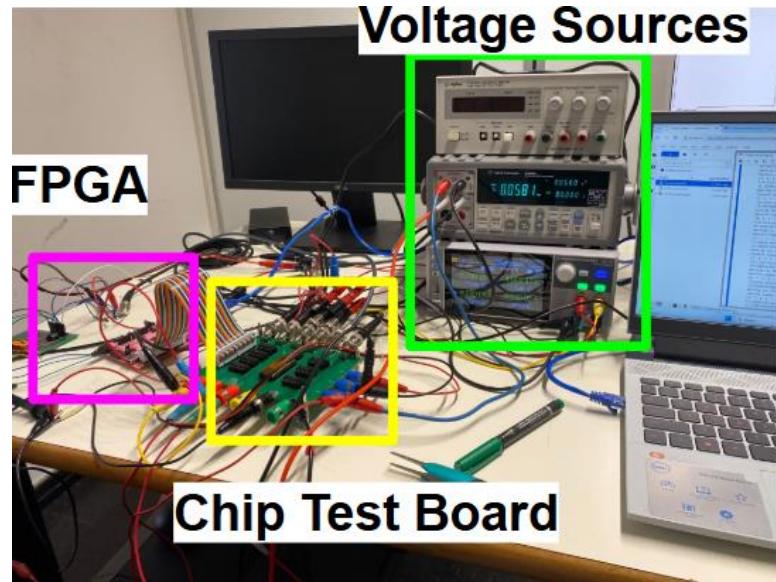

**Figure 19** shows an image of the setup used for measuring the chips. It includes the required voltage sources, the FPGA, and the chip test board.

**Figure 19:** Measurement Setup

### Noise and Offset Results

Noise and offset measurements were taken from 15 fabricated comparator chips to evaluate performance.

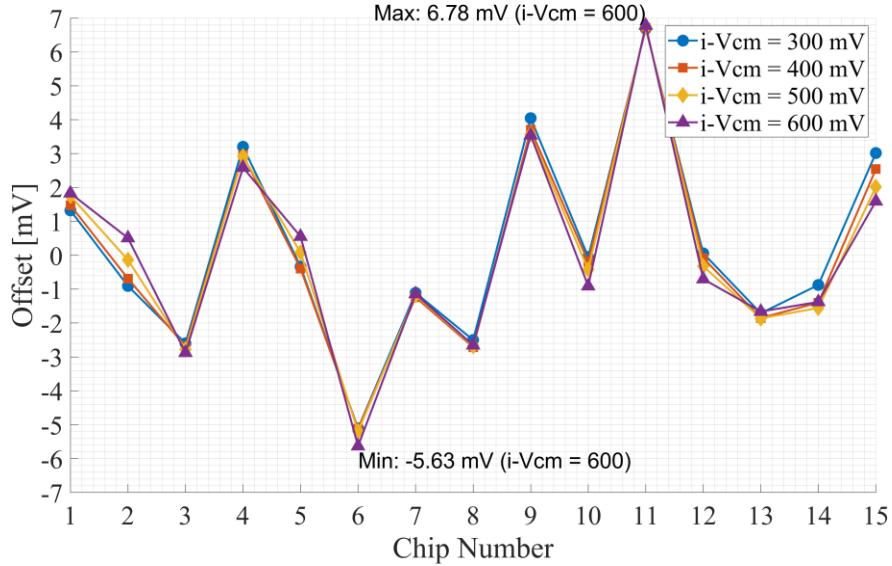

The measured offset voltage for the 15 chips is shown in **Figure 20**, tested under four input common-mode voltages of  $300\text{ mV}$ ,  $400\text{ mV}$ ,  $500\text{ mV}$ , and  $600\text{ mV}$ . The offset values span from a minimum of  $-5.63\text{ mV}$  in chip number 6 to a maximum of  $6.78\text{ mV}$  in chip number 11, both of which occur at  $i\text{-V}_{cm} = 600\text{ mV}$ . Overall, the offset values remain relatively consistent across different  $i\text{-V}_{cm}$  levels for each chip, with only minor variations. Except for chips 2 and 15, where a minor spread on the offset voltage can be seen, suggesting that  $i\text{-V}_{cm}$  changes have minimal impact on offset in most cases.

**Figure 20:** Measured offset in chips for different i-Vcm

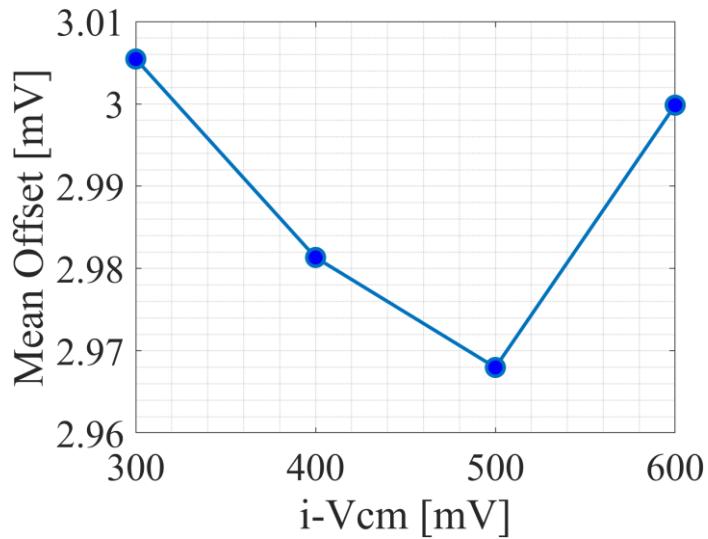

**Figure 21** shows the average offset voltage across all the chips at each input common-mode voltage level. The mean offset decreases as i-Vcm increases, starting from a maximum of 3.006 mV at i-Vcm = 300 mV and reaching a minimum of 2.968 mV at i-Vcm = 500 mV. This trend indicates that the offset voltage in i-Vcm variation is almost imperceptible.

**Figure 21:** Mean offset in chips for different i-Vcm

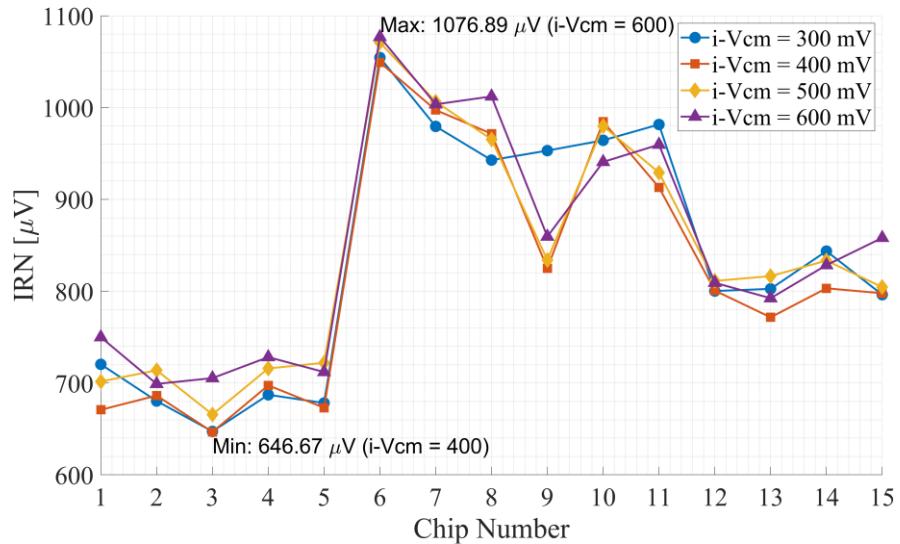

**Figure 22** shows the input-referred noise measurements for the 15 chips, at the four tested input common-mode voltages. The IRN values range from a minimum of 646.67  $\mu$ V at

$i\text{-}V_{cm} = 400 \text{ mV}$  in the chip number 3 to a maximum of  $1076.89 \mu\text{V}$  at  $i\text{-}V_{cm} = 600 \text{ mV}$  in the chip number 6. In contrast to the offset plot, the IRN values for each chip show a more noticeable spread at each  $i\text{-}V_{cm}$  level, indicating that noise is more sensitive to changes in  $i\text{-}V_{cm}$ . However, there is no clear trend in the noise values across  $i\text{-}V_{cm}$  levels. For some chips, a particular  $i\text{-}V_{cm}$  results in minimum noise, while for others, the same  $i\text{-}V_{cm}$  shows maximum noise. This suggests that additional factors beyond  $i\text{-}V_{cm}$  influence noise performance. The variability in noise performance across all chips is also significant, indicating that process variation has an impact on noise as well.

**Figure 22:** Measured noise in chips for different  $i\text{-}V_{cm}$

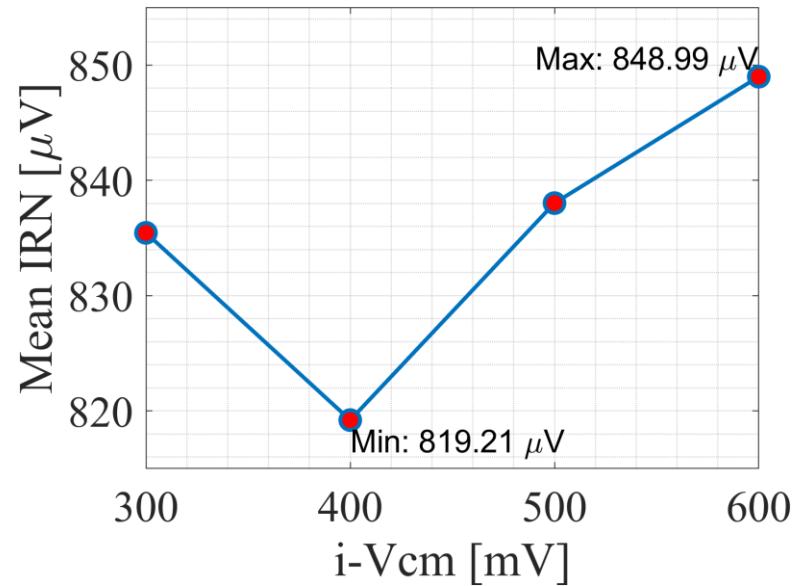

**Figure 23** shows the average noise across the 15 chips at each  $i\text{-}V_{cm}$  level. The mean noise does not change considerably with  $i\text{-}V_{cm}$ . The lowest mean noise is observed at  $i\text{-}V_{cm} = 400 \text{ mV}$ , with a value of  $819.21 \mu\text{V}$ . Noise increases slightly at  $500 \text{ mV}$  and reaches a maximum of  $848.99 \mu\text{V}$  at  $600 \text{ mV}$ . This pattern suggests that noise is lowest around the  $400 \text{ mV}$  input common-mode voltage but increases at higher  $i\text{-}V_{cm}$  levels. Compared to the offset mean plot, this suggests a possible trade-off between offset and noise performance.

**Figure 23:** Mean noise in chips for different i-Vcm

## OFFSET REDUCTION TECHNIQUES, CALIBRATION, AND COMPARATIVE ANALYSIS

### Selected Offset Reduction Techniques

After the measurement of the fabricated chips, the comparator exhibits an offset in the millivolt range, similar to the results seen in simulations. To reduce this offset, a self-calibration technique could be applied. Several offset calibration techniques can be used to achieve this goal. In this case, a load capacitance adjustment method was chosen, where the load capacitance is modified according to the mismatch.

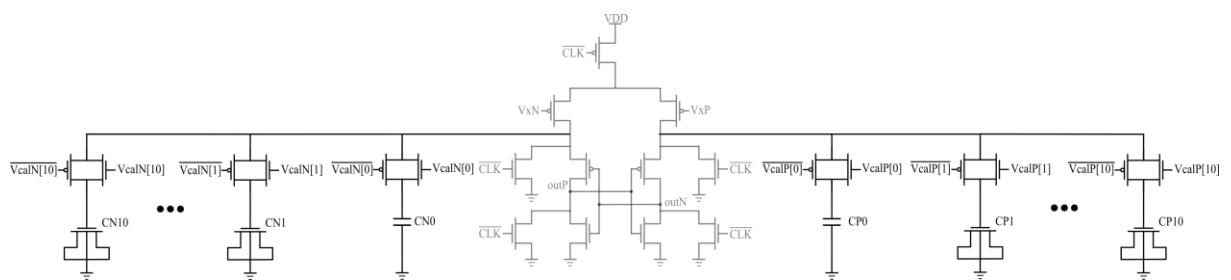

Some modifications to the original comparator design were made in the Output Latch Stage. Adjustments were required, such as the sizing of the input transistors that receive the output signals from the first stage ( $V_{xP}$  and  $V_{xN}$ ) and the head transistor triggered by  $CLK$  signal. To achieve an accurate offset compensation, 22 capacitors were added, as shown in **Figure 24**. Eleven capacitors were placed on each side of the latch in parallel, where each capacitor can be added to the load of the node through the activation of a transmission gate. This setup combines a MIM capacitor ( $C_0$ ) with 10 NMOS transistors ( $C_1-C_{10}$ ) connected as capacitors (Drain-Source-Bulk connected to ground node). The use of a MIM capacitor combined with NMOS capacitors proves effective in reducing silicon area while achieving a fine offset granularity of  $0.5 \text{ mV}$ .

**Figure 24:** Capacitive Load added to the Latch Stage

As shown in **Table 3**, each capacitor compensates for a defined step, with capacitors C1 to C6 capable of being connected to achieve a compensation of up to  $5 \text{ mV}$ . If greater compensation is required, the MIM capacitor C0 can be used as a baseline to provide the same  $5 \text{ mV}$  compensation. Larger capacitors (C7–C10) are designed to provide an incremental increase of approximately  $1 \text{ mV}$  each when connected to the MIM capacitor C0. Without the MIM capacitor, achieving the same granularity would require additional NMOS capacitors, resulting in increased silicon area overhead.

| Capacitor    | Size                                     | Offset Compensation                |

|--------------|------------------------------------------|------------------------------------|

| C0 (MIM-Cap) | $2.3 \mu\text{m} \times 2.3 \mu\text{m}$ | $\sim 5 \text{ mV}$                |

| C1           | $120 \text{ nm} \times 60 \text{ nm}$    | $\sim 0.5 \text{ mV}$              |

| C2           | $120 \text{ nm} \times 60 \text{ nm}$    | $\sim 0.5 \text{ mV}$              |

| C3           | $240 \text{ nm} \times 240 \text{ nm}$   | $\sim 1 \text{ mV}$                |

| C4           | $290 \text{ nm} \times 280 \text{ nm}$   | $\sim 1 \text{ mV}$                |

| C5           | $350 \text{ nm} \times 350 \text{ nm}$   | $\sim 1 \text{ mV}$                |

| C6           | $440 \text{ nm} \times 400 \text{ nm}$   | $\sim 1 \text{ mV}$                |

| C7           | $600 \text{ nm} \times 600 \text{ nm}$   | $\sim 1 \text{ mV}$ (with MIM-Cap) |

| C8           | $750 \text{ nm} \times 750 \text{ nm}$   | $\sim 1 \text{ mV}$ (with MIM-Cap) |

| C9           | $950 \text{ nm} \times 950 \text{ nm}$   | $\sim 1 \text{ mV}$ (with MIM-Cap) |

| C10          | $1.7 \mu\text{m} \times 850 \text{ nm}$  | $\sim 1 \text{ mV}$ (with MIM-Cap) |

**Table 3:** Capacitors size and offset compensation step

To determine the offset direction, the inputs of the comparator are shorted to the same voltage, creating a  $\Delta V_{in} = 0 \text{ mV}$  condition. This setup will indicate which side (OutP or OutN) is stronger due to mismatch, enabling the circuit to apply the calibration technique. The working

principle of the capacitive load technique is based on adjusting the output capacitance to account for mismatch. A capacitance is added to the stronger output side. This additional capacitance slows down the stronger side, by redirecting the current to the capacitor, allowing the weaker side to catch up. As a result, the offset is reduced, shifting it toward the center.

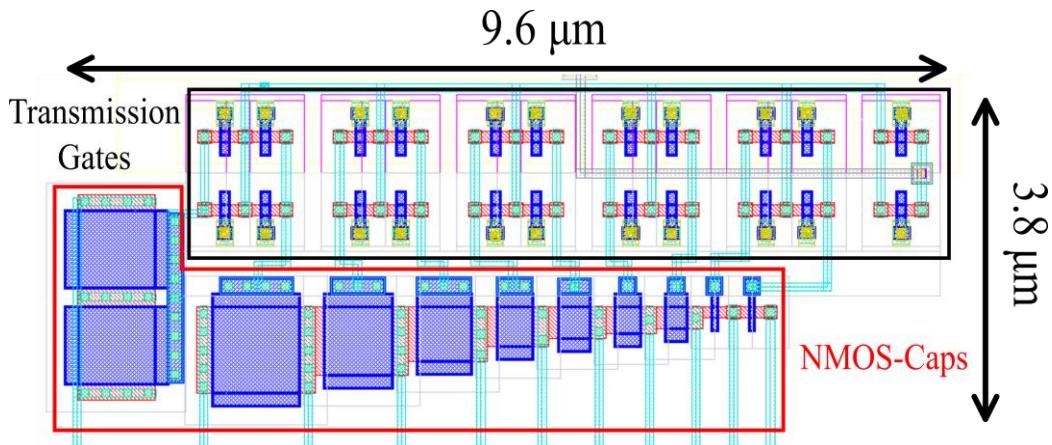

The layout for the additional calibration circuit was also designed. Each side includes 11 transmission gates with a PMOS and an NMOS each, 10 NMOS transistors acting as capacitors, and 1 MIM capacitor, as shown in **Figure 25**. The layout area is  $36.5 \mu\text{m}^2$  per side, resulting in  $73 \mu\text{m}^2$  for both sides. Each MIM capacitor occupies an area of  $5.3 \mu\text{m}^2$  with a total of  $10.6 \mu\text{m}^2$  for both capacitors.

**Figure 25:** Layout Additional Capacitor Calibration Circuit

To compare the presented technique, two other methods were simulated on the same comparator to evaluate their performance and identify their trade-offs. Both methods were tested under the same setup conditions.

The first method, reported in (Jaiswal, et al., 2020), uses a current injection approach with two additional transistors, one on each side, connected in parallel to the input transistors of the output stage, as shown in **Figure 26**. Depending on the offset direction, these extra transistors either increase or decrease current injection to balance the comparator outputs by

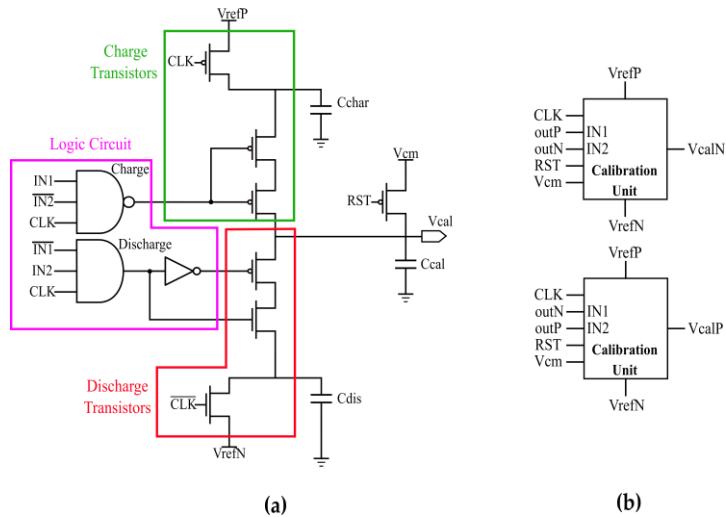

adjusting their gate voltage, which is controlled by the charge pump circuit shown in **Figure 27a**.

**Figure 26:** Additional Transistors in the output stage for Charge Pump approach

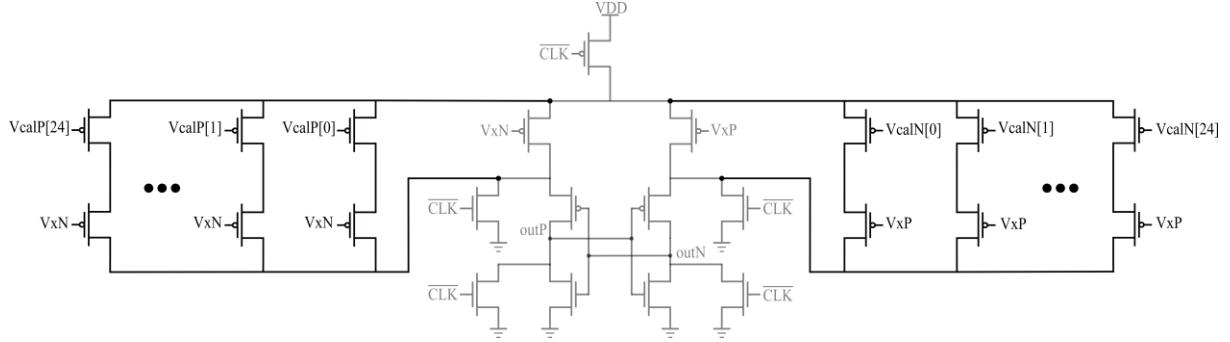

**Figure 27:** Additional Components for the Gate Voltage Control for Charge Pump approach.

a) Charge Pump Circuit. b) Inputs and Outputs of the Charge Pump circuits

A combination of signals IN1, IN2, and CLK is used, to determine the activation of Charge and Discharge nodes, as illustrated in **Figure 27a**. This decision is implemented using a NAND gate for the Charge signal and an AND gate for the Discharge signal. The logic

equations governing the activation of Charge and Discharge signals are given by Equations ( 7 ) and ( 10 ), respectively.

$$Charge = \overline{CLK \cdot IN1 \cdot \overline{IN2}} \quad (7)$$

$$Discharge = CLK \cdot \overline{IN1} \cdot IN2 \quad (8)$$

These signals are activated only when CLK is high and IN1 and IN2 have opposite values.

To control whether VcalP or VcalN needs to increase or decrease, the input signals shown in **Figure 27b** are used. For VcalP, the comparator output outP is connected to IN1, and outN is connected to IN2. Connections are inverted in the case of VcalN, with outN connected to IN1 and outP to IN2. This setup ensures that, based on the comparator outputs, one calibration unit charges while the other discharges.

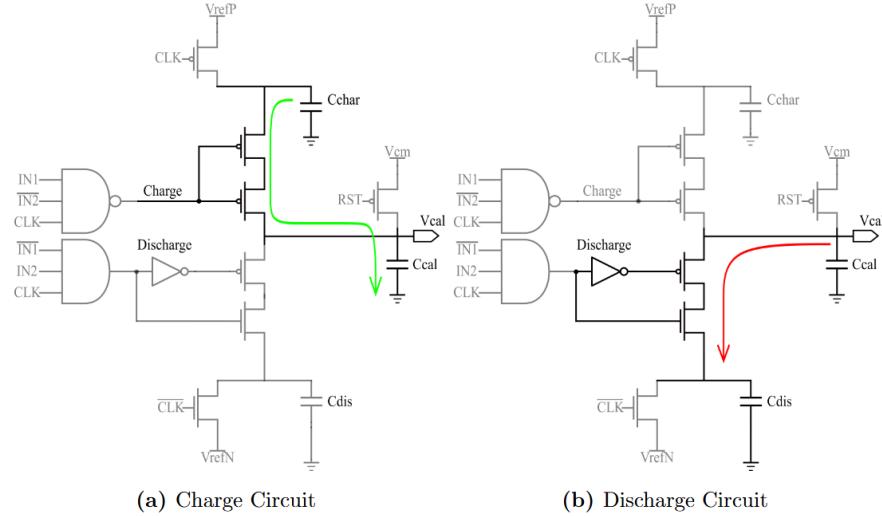

The operation of the charge pump proceeds as follows: the process begins by triggering the RST signal, which sets the capacitor Ccal to an initial voltage corresponding to the circuit's common-mode voltage in this case. When the circuit needs to increase the voltage on Ccal, as illustrated in **Figure 28a**, Cchar is charged to a reference voltage VrefP. After charging, Cchar is connected in parallel with Ccal, creating a slight voltage increase on Vcal due to charge redistribution. Vcal is applied to the gate of the added PMOS transistor, as a result, this voltage increase leads to a controlled reduction in the current flowing into the latch.

Similarly, as one side of the output latch charges, the opposite side discharges. For discharging, as shown in **Figure 28b**, Cdis is connected to a lower reference voltage VrefN. In each clock cycle, Cdis is connected in parallel with Ccal, causing a small reduction in Vcal,

which produces a small increase in current, in contrast to the charging side of the output stage. As a result, this adjustment is applied to the weaker side.

**Figure 28:** Charging and Discharging of the Charge Pump

To determine the required capacitance for  $C_{cal}$ , Equation ( 10 ) was used. This formula is derived from the charge distribution between the capacitors connected in parallel during each clock cycle, based on the reference voltages  $V_{refP}$  and  $V_{refN}$ , as well as the desired voltage step for the gate of the additional transistors in the latch.

$$C_{cal} = C_{char} \cdot \frac{V_{ref} - (V_o + V_{step})}{V_{step}} \quad (9)$$

Where  $V_o$  is the initial voltage for the  $C_{cal}$  capacitor, set to  $V_{cm}$ , and  $V_{step}$  is the chosen voltage increment or decrement for  $V_{calP}$  and  $V_{calN}$ .

In this design,  $V_{refP}$  is set to  $900 \text{ mV}$ , the maximum voltage  $C_{cal}$  can reach, and  $V_{refN}$  is set to  $300 \text{ mV}$ , the minimum voltage for  $C_{cal}$ . The smallest MIM capacitors available in the chosen technology (a 65-nm commercial node) present an area of  $4 \mu\text{m}^2$  and a capacitance of  $5.63 \text{ fF}$ , which are used for  $C_{char}$  and  $C_{dis}$ . The desired gate voltage step is  $2.5 \text{ mV}$ , and the

initial voltage  $V_{cm}$  on both sides is 600 mV. Applying the Equation ( 9 ), the required capacitance for  $C_{cal}$  is calculated in Equation ( 10 ).

$$C_{cal} = 5.63 \cdot 10^{-15} \cdot \frac{0.9 - (0.6 + 0.0025)}{0.0025} = 669.97 fF \quad (10)$$

The layout of the charge pump approach is presented in **Figure 29**. Each side occupies  $19.25 \mu\text{m}^2$ , resulting in a total of  $38.5 \mu\text{m}^2$  for both sides. Additionally, the MIM capacitors require a combined area of  $1266 \mu\text{m}^2$  for six capacitors, with three on each side.

**Figure 29:** Layout Additional Charge Pump Circuit

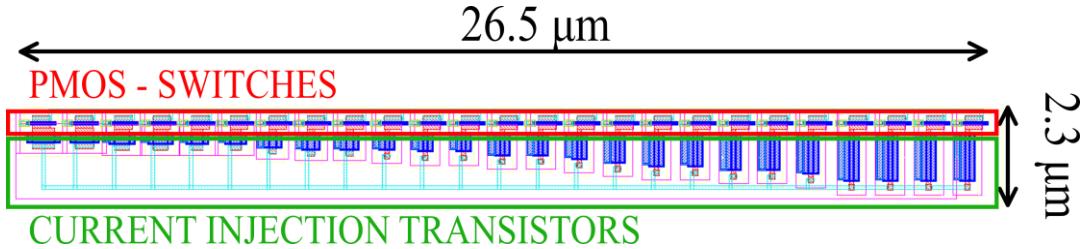

The second method used for comparison is based on the approach reported in (Lee, et al., 2020; Sharma, Srivastava, Hande, Sehgal, & Das, 2023), which also uses current injection with a set of additional transistors. This approach was adapted to the output latch as shown in **Figure 30**, with 25 PMOS transistors on each side, connected in parallel with the input transistors of the output stage. Nodes  $V_{xN}$  and  $V_{xP}$  are used as gate voltage of the additional

transistors. Each transistor includes a PMOS switch that allows it to be attached or detached, depending on the required offset voltage compensation.

**Figure 30:** Parallel transistors added to the Latch Stage

The number of additional transistors was selected based on the desired calibration step size. To achieve a more precise calibration and to make a fair comparison with the proposed method, a step of 0.5 \$mV\$ was chosen. To compensate for offset voltages up to 12.5 \$mV\$, Table \ref{t:transis\_offset} shows the transistor sizes required and their respective contributions to offset voltage compensation. Since the transistors are connected in parallel, the combined current from all connected transistors is injected into the weaker output side, helping to balance the latch outputs by increasing the current on that side.

| Transistor | Size                 | Offset Compensation (Accumulated) |

|------------|----------------------|-----------------------------------|

| 0          | 120 nm x 1.3 $\mu$ m | $\sim 0.5$ mV                     |

| 1          | 120 nm x 1.3 $\mu$ m | $\sim 1$ mV                       |

| 2          | 120 nm x 1.3 $\mu$ m | $\sim 1.5$ mV                     |

| 3          | 120 nm x 1.3 $\mu$ m | $\sim 2$ mV                       |

| 4          | 120 nm x 1.1 $\mu$ m | $\sim 2.5$ mV                     |

| 5          | 120 nm x 1 $\mu$ m   | $\sim 3$ mV                       |

| 6          | 120 nm x 1 $\mu$ m   | $\sim 3.5$ mV                     |

|    |                 |           |

|----|-----------------|-----------|

| 7  | 120 nm x 900 nm | ~ 4 mV    |

| 8  | 120 nm x 900 nm | ~ 4.5 mV  |

| 9  | 120 nm x 800 nm | ~ 5 mV    |

| 10 | 120 nm x 700 nm | ~ 5.5 mV  |

| 11 | 120 nm x 600 nm | ~ 6 mV    |

| 12 | 120 nm x 600 nm | ~ 6.5 mV  |

| 13 | 120 nm x 500 nm | ~ 7 mV    |

| 14 | 120 nm x 500 nm | ~ 7.5 mV  |

| 15 | 120 nm x 450 nm | ~ 8 mV    |

| 16 | 200 nm x 450 nm | ~ 8.5 mV  |

| 17 | 200 nm x 450 nm | ~ 9 mV    |

| 18 | 200 nm x 400 nm | ~ 9.5 mV  |

| 19 | 300 nm x 300 nm | ~ 10 mV   |

| 20 | 300 nm x 300 nm | ~ 10.5 mV |

| 21 | 400 nm x 300 nm | ~ 11 mV   |

| 22 | 400 nm x 300 nm | ~ 11.5 mV |

| 23 | 500 nm x 250 nm | ~ 12 mV   |

| 24 | 600 nm x 250 nm | ~ 12.5 mV |

**Table 4:** Transistors size and offset compensation step

The layout of the parallel transistor approach is shown in **Figure 31**. Each side occupies  $61 \mu\text{m}^2$ , resulting in a total of  $122 \mu\text{m}^2$  for both sides.

**Figure 31:** Layout Additional Parallel Transistors approach

### Calibration Process

To verify the effectiveness of the calibration technique, two distinct calibration algorithms were implemented and simulated. The first algorithm referred to as the "fast method", prioritizes speed by completing calibration as soon as the first output transition is detected, using a reduced number of clock cycles; however, this comes at the cost of precision. This method was used in works (Tsirmpas, Kontelis, Souliotis, & Plessas, 2024; Jaiswal, et al., 2020; Lee, et al., 2020; Sharma, Srivastava, Hande, Sehgal, & Das, 2023).

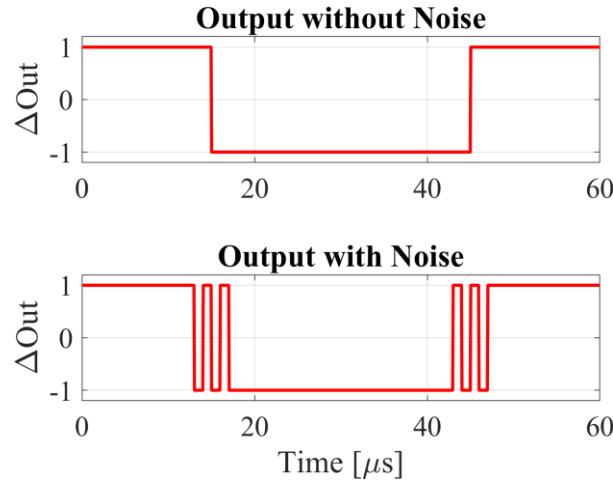

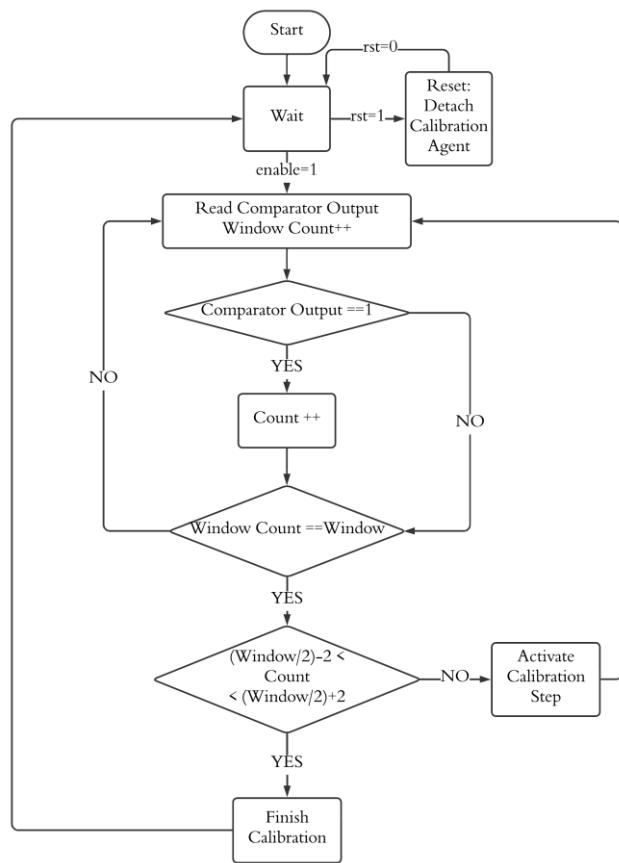

When the differential input approaches the offset voltage, the outputs of the comparator present oscillations, as shown in **Figure 32**, where the differential output is compared for cases with and without noise. This behavior complicates calibration, as relying on the first output transition to signal calibration completion may lead to insufficient compensation. The initial transition could be noise-induced, with subsequent outputs returning to their previous state, failing to achieve proper calibration.

To mitigate the effects of the noise, the second algorithm, referred to as the "window-based method" is proposed. This method evaluates a predetermined number of outputs and analyzes whether the result alternates approximately evenly between the two comparator outputs. This minimizes the impact of noise and ensures that the calibrated offset voltage is as near to zero as possible.

**Figure 32:** Noise Effect in the Comparator Output

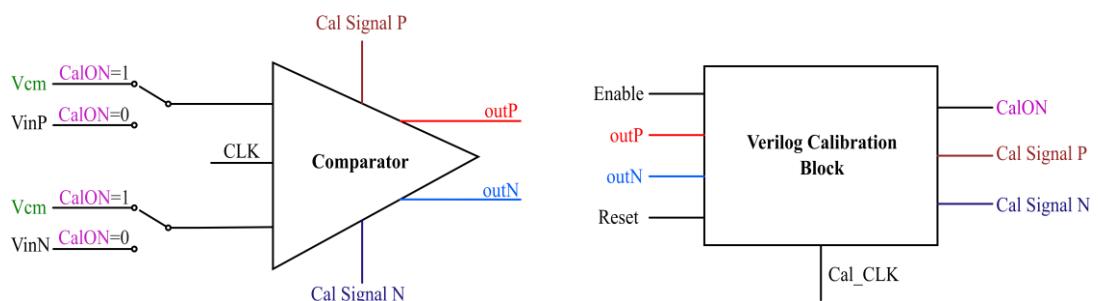

The two algorithms are implemented in synthesizable Verilog code, enabling fabrication of the digital block. Performance is tested using the Analog-Mixed Signal (AMS) simulator in Virtuoso, which performs real-time co-simulation between the digital and analog components (Castaldo & Gibilaro, 2024). **Figure 33** illustrates the setup, where the Verilog Calibration Block inputs include: "Enable", which triggers the calibration; "Reset", which restores the comparator to its pre-calibration state; "outP" and "outN", which indicate the comparator's output state; and "Cal\_CLK", a clock signal with the same frequency as the comparator clock but phase-shifted by 1/4 of the period to ensure stable output analysis.

**Figure 33:** Simulation Setup of the Comparator with the Calibration Block

The outputs are: "CalON", which connects the comparator inputs to Vcm when high ("1") and to VinP and VinN when low ("0"); and "Cal Signal P" and "Cal Signal N", which activate the compensation technique. For the capacitive load method, these correspond to signals VcalP[0:11] and VcalN[0:11], activating transmission gates to connect calibration capacitors. In the charge pump method, they control the Calibration Unit clock, and in the parallel transistors method, they represent signals VcalP[0:24] and VcalN[0:24], which activate or deactivate the MOS switches.

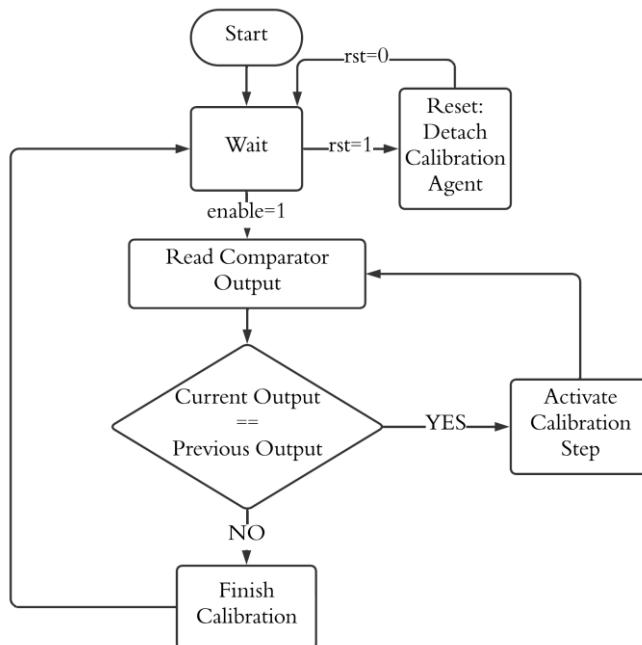

In **Figure 34**, the flowchart of the fast algorithm is shown. This method analyzes the comparator outputs to identify the stronger side due to mismatch and subsequently activates the calibration mechanism. After each activation, the outputs are re-evaluated in the next clock cycle. If the output is the same as the previous one, the algorithm continues the calibration process. However, if the output changes, the algorithm considers that the calibration is complete.

**Figure 34:** Fast Calibration Method Flowchart

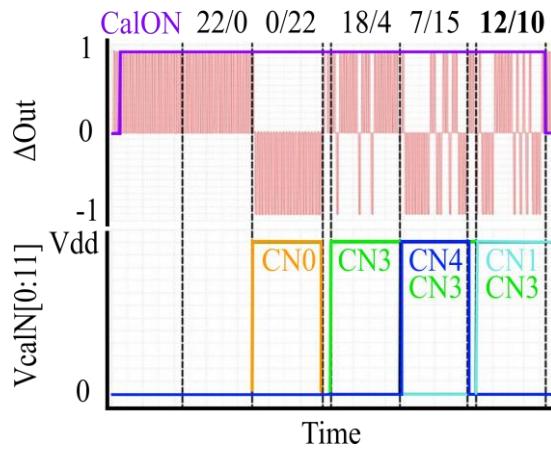

Using the Fast Algorithm, which only checks if the current output matches the previous one, the capacitors are activated in order from the smallest to the largest compensation step. **Figure 35** shows an example of a Monte Carlo simulation with an offset of approximately 7 mV. At the start, an enable signal activates the calibration, and the "CalON" signal indicates that the process has started, connecting the comparator inputs to the same voltage, setting  $\Delta V_{in}$  to 0.

**Figure 35:** Fast Calibration Method Example

During Step 1, the smallest capacitors (CN1 - CN6) are connected sequentially. These capacitors are designed to compensate for offsets of up to 5 mV. However, since the offset exceeds this range, CN1 - CN6 capacitors are disconnected in Step 2. In Step 3, the larger capacitors are connected, starting with CN0 (MIM capacitor), followed by CN7, and finally CN8. In Step 4, when CN8 is connected, the output logic level reverses compared to the previous state, signaling that the calibration is complete. At this stage, "CalON" is deactivated, marking the end of the calibration process.

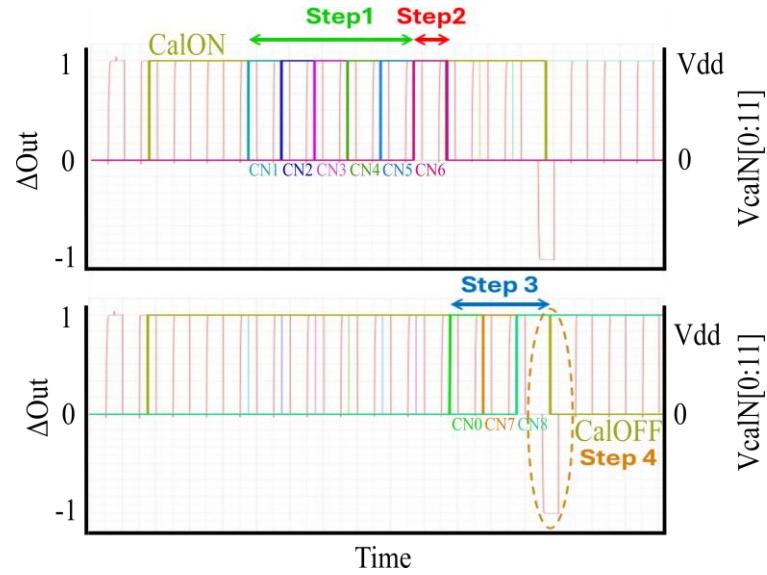

The flowchart in **Figure 36** describes the window-based algorithm that exploits the noise present in the circuit. In this method, a fixed number of output readings referred to as

"Window" is set, and the algorithm triggers the comparator and stores a count of the outputs for "Window" times. Afterward, it checks how many of these outputs are "1" and the algorithm verifies whether the total "Count" of 1's falls within a predefined range. This range is set to  $\text{Window}/2 \pm 2$ . For example, if "Window" is set to 22, an acceptable range for "Count" would be from 9 to 13, as shown in the flowchart. If the "Count" is outside this range, the algorithm proceeds to the next calibration step and repeats the process until the "Count" falls within the desired range, indicating that the offset of the comparator is sufficiently low for the outputs to toggle between logic '1' and '0' due to noise fluctuations. At this point, the calibration is considered to be complete.

**Figure 36:** Window Calibration Method Flow Chart