**UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ**

**Colegio de Posgrados**

**Non-Volatile Content-Addressable Memory for Energy-Efficient & High Performance Search and Update Operations**

**Mecanismo de Titulación: Tesis en torno a una hipótesis o problema de investigación y su contrastación**

**Alessandro Salvatore Bedoya Aliatis**

**Marco Lanuzza, Doctor of Philosophy

Esteban Garzón, Doctor of Philosophy

Director de Trabajo de Titulación**

Trabajo de titulación de posgrado presentado como requisito para la obtención del título de Magíster en Nanoelectrónica

Quito, marzo de 2025

**UNIVERSIDAD SAN FRANCISCO DE QUITO USFQ**

**COLEGIO DE POSGRADOS**

**HOJA DE APROBACIÓN DE TRABAJO DE TITULACIÓN**

**Non-Volatile Content-Addressable Memory for Energy-Efficient & High Performance Search and Update Operations**

**Alessandro Salvatore Bedoya Aliatis**

Nombre del Director del Programa:

**Luis Miguel Prócel**

Título académico:

**Doctor of Philosophy**

Director del programa de:

**Maestría en Nanoelectrónica**

Nombre del Decano del colegio Académico:

**Eduardo Alba**

Título académico:

**Doctor of Philosophy**

Decano del Colegio:

**Colegio de Ciencias e Ingenierías**

Nombre del Decano del Colegio de Posgrados:

**Dario Niebieskikwiat**

Título académico:

**Doctor of Physics**

**Quito, marzo 2025**

## © DERECHOS DE AUTOR

Por medio del presente documento certifico que he leído todas las Políticas y Manuales de la Universidad San Francisco de Quito USFQ, incluyendo la Política de Propiedad Intelectual USFQ, y estoy de acuerdo con su contenido, por lo que los derechos de propiedad intelectual del presente trabajo quedan sujetos a lo dispuesto en esas Políticas.

Asimismo, autorizo a la USFQ para que realice la digitalización y publicación de este trabajo en el repositorio virtual, de conformidad a lo dispuesto en la Ley Orgánica de Educación Superior del Ecuador.

Nombre del estudiante: Alessandro Salvatore Bedoya Aliaits

Código de estudiante: 00335270

C.I.: 1726295841

Lugar y fecha: Quito, 03 de marzo de 2025.

## ACLARACIÓN PARA PUBLICACIÓN

**Nota:** El presente trabajo, en su totalidad o cualquiera de sus partes, no debe ser considerado como una publicación, incluso a pesar de estar disponible sin restricciones a través de un repositorio institucional. Esta declaración se alinea con las prácticas y recomendaciones presentadas por el Committee on Publication Ethics COPE descritas por Barbour et al. (2017) Discussion document on best practice for issues around theses publishing, disponible en <http://bit.ly/COPETheses>.

## UNPUBLISHED DOCUMENT

**Note:** The following graduation project is available through Universidad San Francisco de Quito USFQ institutional repository. Nonetheless, this project – in whole or in part – should not be considered a publication. This statement follows the recommendations presented by the Committee on Publication Ethics COPE described by Barbour et al. (2017) Discussion document on best practice for issues around theses publishing available on <http://bit.ly/COPETheses>.

**DEDICATORIA**

To my parents, who always encouraged me to get a Masters Degree, this work

is your fault.

## RESUMEN

Dispositivos emergentes como los “double-barrier magnetic tunnel junction” (DMTJ) son candidatos prometedores para enfrentar problemas como el “muro de memoria” y “muro de potencia” de los sistemas informáticos modernos. Los DMTJ ofrecen altas velocidades de escritura y lectura, gran escalabilidad e integración con tecnología CMOS. Por ende son altamente considerados para sistemas informáticos centrados en la memoria, como las “Content Addressable Memories” (CAM), que han tenido éxito comercial en sistemas de redes de alta velocidad. Este trabajo presenta una celda de memoria CAM basada en dispositivos MTJ no volátiles (NV-CAM). Nuestro diseño presenta operaciones de búsqueda y escritura a alta velocidad y bajo consumo. Esto permite utilizarla en aplicaciones que requieren un elevado número de búsquedas/escrituras, como los procesadores asociativos. La celda CMOS/DMTJ propuesta se diseñó utilizando una tecnología CMOS comercial de 65nm y un modelo compacto DMTJ escrito en Verilog-A. A través de una evaluación de la celda mediante simulaciones Montecarlo se obtienen figuras de mérito competitivas en comparación con el estado del arte. Para obtener comparaciones justas, se caracterizaron otras celdas presentadas en la literatura utilizando la misma tecnología y modelo de dispositivo. Nuestra NV-CAM presenta una mejora en los retardos de búsqueda y escritura de alrededor del 75% y 71% respectivamente..

Palabras clave: Content Addressable Memory, CAM, CAM no volátil, unión túnel magnética de doble barrera, DMTJ.

## ABSTRACT

Novel devices such as the double-barrier magnetic tunnel junction (DMTJ) are promising candidates to address the current “Memory Wall” and “Power Wall” challenges in modern computing systems. DMTJs feature high write/read speeds, great scalability and integration with CMOS. As such, they are often considered for memory-centric computing systems like Content-Addressable Memories (CAM), which provide a highly parallel in-memory matching operation that has found commercial success in high-speed network systems. This work presents a non-volatile content addressable memory (NV-CAM) based DMTJ technology. Our design features energy-efficient, high performance search and update operations. This enables applications that require a high number of searches/updates, such as associative processors. The proposed CMOS/DMTJ hybrid cell was designed using a commercial 65nm CMOS technology and a Verilog-A based DMTJ compact model. Evaluation of the cell through Montecarlo simulations produce competitive figures of merit when compared to the state of the art. For the sake of fair comparisons, other cells presented in literature were characterized using the same transistor technology and device mode. Our NV-CAM presents an improvement in search and update delays of about 75% and 71% respectively..

**Key words:** Content-addressable memory, CAM, Non-Volatile CAM, double-barrier magnetic tunnel junction, DMTJ.

# Contents

|                                                               |           |

|---------------------------------------------------------------|-----------|

| <b>Contents</b>                                               | <b>8</b>  |

| <b>List of Figures</b>                                        | <b>10</b> |

| <b>List of Tables</b>                                         | <b>11</b> |

| <b>1 List of Abbreviations</b>                                | <b>12</b> |

| <b>2 Introduction</b>                                         | <b>15</b> |

| 2.1 Introduction & Motivation . . . . .                       | 15        |

| 2.2 Conventional & Emerging Non-Volatile Memory Technologies  |           |

| For Content-Addressable Memories . . . . .                    | 16        |

| 2.2.1 Resistive Random Access Memory (ReRAM) . . . . .        | 17        |

| 2.2.2 Phase Change Memory (PCM) . . . . .                     | 19        |

| 2.2.3 Ferroelectric Field Effect Transistor (FeFET) . . . . . | 20        |

| 2.2.4 Magneric Random Access Memories (MRAM) . . . . .        | 21        |

| Single-Barrier Magnetic Tunnel Junctions (SMTJ) . . . . .     | 22        |

| Double-Barrier Magnetic Tunnel Junction (DMTJ) . . . . .      | 23        |

| 2.3 Organization of the Thesis . . . . .                      | 25        |

| <b>3 Background</b>                                           | <b>26</b> |

| 3.1 Content Addressable Memories . . . . .                    | 26        |

| 3.1.1 CMOS CAMs . . . . .                                     | 28        |

| 3.1.2 Non-Volatile CAMs Based on STT-MRAM Technology .        | 30        |

| Voltage Divider Structures . . . . .                          | 31        |

| Latch Based Structures . . . . .                              | 32        |

| 3.2 Non-Volatile CAMs Application Space . . . . .             | 32        |

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>4 Non-Volatile Content-Addressable Memory (NV-CAM) Design</b> | <b>36</b> |

| 4.0.1 Overview of the MTJ Compact Model . . . . .                | 36        |

| 4.1 17T4MTJ Cell Structure . . . . .                             | 37        |

| 4.2 Cell Operation . . . . .                                     | 39        |

| 4.2.1 Write Operation . . . . .                                  | 39        |

| 4.2.2 Search Operation . . . . .                                 | 41        |

| 4.3 Performance Analysis . . . . .                               | 44        |

| <b>5 Alternative NV-CAM Cell Architectures</b>                   | <b>51</b> |

| 5.1 Overview of Alternative Cells . . . . .                      | 51        |

| 5.2 9T2MTJ . . . . .                                             | 51        |

| 5.2.1 Cell Schematic and Operating Principles . . . . .          | 51        |

| 5.2.2 Design and Discussion . . . . .                            | 54        |

| 5.3 10T4MTJ . . . . .                                            | 55        |

| 5.3.1 Cell Schematic and Operating Principles . . . . .          | 55        |

| 5.3.2 Design and Discussion . . . . .                            | 59        |

| 5.4 10T2MTJ . . . . .                                            | 60        |

| 5.4.1 Cell Schematic and Operating Principles . . . . .          | 60        |

| 5.4.2 Design and Discussion . . . . .                            | 63        |

| 5.5 Performance Comparison . . . . .                             | 64        |

| <b>6 Conclusion</b>                                              | <b>67</b> |

| 6.1 Conclusion . . . . .                                         | 67        |

| 6.2 Research Output . . . . .                                    | 68        |

# List of Figures

|     |                                                |    |

|-----|------------------------------------------------|----|

| 2.1 | Emergent Non-Volatile Devices . . . . .        | 17 |

| 2.2 | Double Barrier MTJ . . . . .                   | 24 |

| 3.1 | CAM Block Diagram . . . . .                    | 27 |

| 3.2 | CAM Taxonomy . . . . .                         | 28 |

| 3.3 | NOR CMOS Cell and Matchline . . . . .          | 29 |

| 3.4 | NAND CMOS Cell and Matchline . . . . .         | 30 |

| 3.5 | 2T2MTJ Circuit Diagram . . . . .               | 31 |

| 3.6 | STT–MRAM NV-CAM Top Level Diagram . . . . .    | 32 |

| 3.7 | AP Architecture Diagram . . . . .              | 34 |

| 4.1 | 17T4MTJ Circuit Diagram . . . . .              | 38 |

| 4.2 | 17T4MTJ Write Circuit Diagrams . . . . .       | 39 |

| 4.3 | 17T4MTJ Write Timing Diagram . . . . .         | 40 |

| 4.4 | 17T4MTJ Search Circuit Diagrams . . . . .      | 42 |

| 4.5 | 17T4MTJ Search Timing Diagram . . . . .        | 43 |

| 4.6 | 17T4MTJ cell Layout . . . . .                  | 45 |

| 4.7 | Hybrid 3D CMOS/MTJ Process . . . . .           | 46 |

| 4.8 | 17T4MTJ Performance Evaluation Setup . . . . . | 47 |

| 4.9 | 17T4MTJ cell Performance Evaluation . . . . .  | 48 |

| 5.1 | 9T2MTJ Circuit Diagram . . . . .               | 52 |

| 5.2 | 10T4MTJ Circuit Diagram . . . . .              | 56 |

| 5.3 | 10T2MTJ Circuit Diagram . . . . .              | 61 |

# List of Tables

|      |                                                 |    |

|------|-------------------------------------------------|----|

| 4.1  | DMTJ device parameters . . . . .                | 37 |

| 4.2  | MAB data encoding . . . . .                     | 38 |

| 4.3  | 17T4MTJ cell write operations . . . . .         | 41 |

| 4.4  | 17T4MTJ cell search operations . . . . .        | 44 |

| 4.5  | 17T4MTJ cell search results . . . . .           | 49 |

| 4.6  | 17T4MTJ cell write results . . . . .            | 50 |

| 5.1  | 9T2MTJ cell write operations . . . . .          | 53 |

| 5.2  | 9T2MTJ cell search operations . . . . .         | 53 |

| 5.3  | 9T2MTJ transistor sizes . . . . .               | 54 |

| 5.4  | 10T4MTJ cell write operations . . . . .         | 57 |

| 5.5  | 10T4MTJ cell search operations . . . . .        | 58 |

| 5.6  | 10T4MTJ transistor sizes . . . . .              | 59 |

| 5.7  | 10T2MTJ cell write operations . . . . .         | 61 |

| 5.8  | 10T2MTJ NV-CAM cell search operations . . . . . | 62 |

| 5.9  | 10T2MTJ transistor sizes . . . . .              | 63 |

| 5.10 | NV-CAMs Figures of merit . . . . .              | 65 |

# Chapter 1

## List of Abbreviations

|              |                                          |

|--------------|------------------------------------------|

| <b>ACAM</b>  | Analog Content Addressable Memory        |

| <b>ACS</b>   | Associative Computing Systems            |

| <b>AP</b>    | Associative Processor                    |

| <b>BCAM</b>  | Binary Content Addressable Memory        |

| <b>BEOL</b>  | Back End Of Line                         |

| <b>CAM</b>   | Content Addressable Memory               |

| <b>CBRAM</b> | Conductive Bridging Random Access Memory |

| <b>CCL</b>   | Cross-Coupled Latch                      |

| <b>CL</b>    | Comparison Logic                         |

| <b>DMTJ</b>  | Double Barrier Magnetic Tunnel Junction  |

| <b>DRAM</b>  | Dynamic Random Access Memory             |

| <b>DSA</b>   | Differential Sense Amplifier             |

| <b>EC</b>    | Coercive Electric Field                  |

| <b>FDSOI</b> | Fully-Depleted Silicon On Insulator      |

| <b>FE</b>    | Ferroelectric Layer                      |

| <b>FeFET</b> | Ferroelectric Field Effect Transistor    |

|             |                                             |

|-------------|---------------------------------------------|

| <b>FEOL</b> | Front End Of Line                           |

| <b>FIMS</b> | Field Induced Magnetic Switching            |

| <b>FL</b>   | Free Layer                                  |

| <b>FM</b>   | Ferromagnetic Layer                         |

| <b>FOM</b>  | Figures Of Merit                            |

| <b>FPGA</b> | Field Programmable Gate Array               |

| <b>HDD</b>  | Hard Disk Drive                             |

| <b>HKMG</b> | High-K Metal Gate                           |

| <b>HPC</b>  | High Performance Computing                  |

| <b>HRS</b>  | High Resistance State                       |

| <b>IL</b>   | Interfacial Layer                           |

| <b>IMC</b>  | In-Memory Computing                         |

| <b>LRS</b>  | Low Resistance State                        |

| <b>MAB</b>  | Memory Array Block                          |

| <b>MFIS</b> | Metal–Ferroelectric–Insulator–Semiconductor |

| <b>MFS</b>  | Metal–Ferroelectric–Semiconductor           |

| <b>ML</b>   | MatchLine                                   |

| <b>MLC</b>  | Multi–Level Cell                            |

| <b>MLS</b>  | Match-Line Sensing Network                  |

| <b>MLSA</b> | Matchline Sense Amplifier                   |

| <b>MRAM</b> | Magnetic Random Access Memory               |

| <b>MSN</b>  | Matchline Switching Network                 |

| <b>MTJ</b>  | Magnetic Tunnel Junction                    |

|              |                                            |

|--------------|--------------------------------------------|

| <b>MW</b>    | Memory Window                              |

| <b>NVCAM</b> | Non-Volatile Content Addressable Memory    |

| <b>NVM</b>   | Non-Volatile Memory                        |

| <b>OxRAM</b> | Metal Oxide Resistive Random Access Memory |

| <b>PCM</b>   | Phase Change Memory                        |

| <b>PDF</b>   | Probability Density Function               |

| <b>PDK</b>   | Process Design Kit                         |

| <b>PL</b>    | Pinned Layer                               |

| <b>PLA</b>   | Programmable Logic Array                   |

| <b>PU</b>    | Processing Unit                            |

| <b>PUF</b>   | Physically Unclonable Function             |

| <b>ReRAM</b> | Resistive Random Access Memory             |

| <b>SA</b>    | Sense Amplifier                            |

| <b>SER</b>   | Search Error Rate                          |

| <b>SIMD</b>  | Single-Instruction-Multiple-Data           |

| <b>SN</b>    | Search Logic Network                       |

| <b>SOT</b>   | Spin Orbit Torque                          |

| <b>STT</b>   | Spin Transfer Torque                       |

| <b>TCAM</b>  | Ternary Content Addressable Memory         |

| <b>TMR</b>   | Tunnel MagnetoResistance                   |

| <b>VCMA</b>  | Voltage Controlled Magnetic Anisotropy     |

| <b>VDN</b>   | Voltage Divider Network                    |

| <b>WER</b>   | Write Error Rate                           |

# Chapter 2

## Introduction

### 2.1 Introduction & Motivation

Computing systems based on Von Neumann architecture present a data-transfer bottleneck, caused by the increasing disparity between the processing units and the relatively slower access times of main memory. This is often referred to as the “memory wall” [1]. Moore’s Law has further aggravated this bottleneck throughout the past decade. The increase in transistor density, accompanied by the exponential rise in leakage current due to scaling down voltage and feature sizes in advanced technology nodes, has created critical power dissipation challenges that threaten to exhaust the capabilities of conventional cooling solutions, a problem known as the “power wall” [2].

In-Memory computing (IMC) rises as an alternative to overcome the “memory wall”, operating in-situ, employing the memory cells for storage and processing [3], without the need for data movement. One of such IMC approaches are Content Addressable Memories (CAMs), which provide a highly parallel in-memory matching operation that has found commercial success in high-speed network systems [4]. CAMs are non-random access memory structures where an input query word is looked into the entire memory content, signaling the matching data [5]. CAMs implement two basic operations. The write operation stores/updates information in the memory array, while the search operation compares the input query word to every stored entry/word simultaneously, obtaining the matching address or addresses during a single clock cycle. CAMs show promising characteristics for a diverse range of applications such as finite

state machines, pattern matching, and associative computing [6].

While novel system architectures based on conventional CMOS technology can partially alleviate the “memory wall” and “power wall” problems, they still require novel devices to fully address these challenges. Non-volatile emergent memory devices such as the STT-MRAM feature zero standby leakage, high write/read speeds, great scalability and integration density [7]. As such, they are considered promising candidates to realize memory-centric computing systems [8].

## 2.2 Conventional & Emerging Non-Volatile Memory Technologies For Content-Addressable Memories

Non-Volatile CAMs (NV-CAMs) can be built from various emerging non-volatile memory (NVM) devices. These devices include two-terminal switching elements such as Phase Change Memories (PCM), Resistive Random Access Memories (ReRAM) and Magnetic Random Access Memories (MRAM), as well as the three terminal Ferroelectric Field Effect Transistor (FeFET). Ongoing research on these technologies is driven by the potential to offer significant advantages over traditional memory solutions such as transistor-based SRAM and non-volatile Flash. One key advantage of these emerging NVMs is scalability, which allows for the development of high-density memory architectures such as crossbar arrays [9].

PCM, ReRAM, and MRAM devices are fabricated using the back-end of line (BEOL) processes, where the devices are integrated between metal layers. This method of integration facilitates compatibility with existing CMOS technology, a factor which is crucial for their effective application in IMC architectures [10], [11], [12]. On the other hand, the FeFET is fabricated using front-end-of-line (FEOL) processes, which involve different material requirements. Hafnium oxide ( $\text{HfO}_2$ )-based FeFET devices exhibit full CMOS compatibility due to the massive use of  $\text{HfO}_2$  in the fabrication of high-k metal gate (HKMG) MOSFETs introduced by Intel in the 45nm node back in 2007 [13].

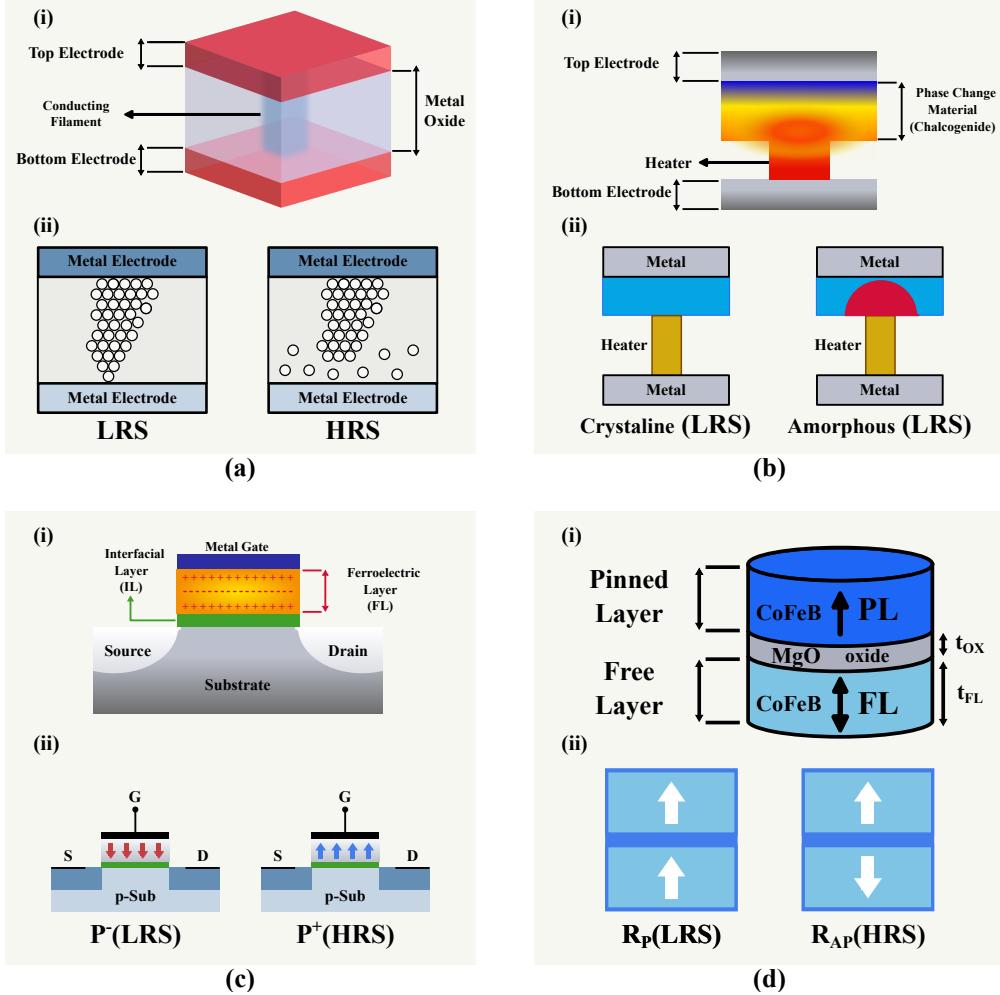

Figure 2.1: Promising emergent non-volatile storage devices. (a) Resistive Random Access Memories, (b) Phase Change Memories, (c) Ferroelectric Field Effect Transistor, and (d) Magnetic Tunnel Junction.

### 2.2.1 Resistive Random Access Memory (ReRAM)

ReRAM research began in the 1960s with the study of the conductive properties of numerous metal oxides, but the potential of these devices as a scalable alternative to existing volatile and NV memories finally picked up during the 2000s [14]. For the past 20 years, ReRAMs have been studied for several applications including in-memory computing [15], cryptography, Physically Unclonable Functions (PUFs) [16], and neuromorphic circuits [17]. Resistive memory technologies have been developed by industrial players for high-density stand-alone memories such as SandDisk’s 32Gb memory device integrated with 24nm technology [18]. Additionally, Panasonic [19], Intel [20] and TSMC [21] have

showcased ReRAM integration as an embedded non-volatile memory (eNVM) alternative.

Although all of the devices discussed in this section are resistive in nature, the term ReRAM is typically used for insulator-based stacks with a defect-based switching mechanism [14]. The structure of a typical ReRAM cell is shown in Fig. 2.1 (a), and consists of an oxide layer sandwiched between two metal contacts. The oxide acts as an insulator, resulting in a high resistance across the ReRAM cell. A localized conductive filament is used to store the state of the device. When the filament is fully set, it forms a path that connects the top and bottom metal electrodes, corresponding to a Low Resistance State (LRS). On the other hand, if part of the filament is destroyed, the ReRAM is in a High Resistance State (HRS).

According to the type of defect used in the switching media, the device is classified into an Oxide ReRAM (OxRAM) or Conductive Bridging ReRAM (CBRAM). ReRAM switching is based on reduction-oxidation (redox) processes caused by fast-moving ions like oxygen vacancies in the case of OxRAM and highly diffusive metal ions like copper or silver in the case of CBRAM.

To obtain a working device, every cell has to undergo a process called FORMING in which the filament is created by applying a high voltage. This process constitutes a practical limitation for integration with different selector devices (like CMOS transistors), since the FORMING voltage may be too high for some technology nodes [14]. Once the filament is created, the cells can switch between the LR and HR states by recreating (SET) and breaking (RESET) the conductive path.

In terms of performance, the speed of the set/reset operation has been shown to span the  $10\text{ns}$  -  $100\mu\text{s}$  range with a typical endurance of  $10^6$  cycles [9]. The dielectric layer is progressively damaged during switching operations, causing an eventual failure due to dielectric breakdown. ReRAM devices are also limited by the switching current (usually greater than  $10\mu\text{A}$ ) as data retention is heavily degraded at lower values, resulting in room temperature data loss within seconds [14].

### 2.2.2 Phase Change Memory (PCM)

Phase change memory research began in 1968 when a fast, reversible switching effect was observed in  $\text{Si}_{12}\text{Te}_{48}\text{As}_{30}\text{Ge}_{10}$  (STAG) material compositions [22]. However, difficulties due to device degradation and instability slowed down progress. PCMs exploit the phase change properties of chalcogenide glasses, and new alloys like  $\text{GeTe-Sb}_2\text{Te}_3$  [23] led to renewed interest in the technology from the early 2000s [24]. Academic literature on phase change memories has focused on various applications including its use as a storage class memory replacement [9], content addressable memories [25] and neuromorphic systems [17]. In the last decade, PCM technology has also been adopted by the industry with Micron announcing massive production in 2012 [26], and Samsung producing an 8 Gbit chip in 20nm technology [27].

In a PCM cell, the crystal switches between two states (phases); an amorphous state (HR phase) where the resistance is high, and a polycrystalline state (LR phase) that shows a low resistance. The structure of a typical PCM cell is shown in Fig. 2.1 (b). The phase change material, typically a Chalcogenide glass, is connected to a metal electrode on one side, and a resistive heating element (metal heater) on the other side. The heater is connected to a second metal electrode, and it is activated by sending a current into the device.

To switch between states, a voltage pulse is applied. To write a '0' (RESET) the cell receives a short high-voltage pulse heating the crystal and causing it to switch from a polycrystalline state to an amorphous state. The reverse process of writing a '1' (SET) requires a long low amplitude pulse that causes the material to revert to a polycrystalline state. The RESET process consumes high power (and energy) while the longer SET process limits the writing speed of the cell [9]. In addition to the extreme states, it is possible to cause the cell to switch to several intermediate stages, allowing the storage of multiple bits per cell in what is called a multi-level cell (MLC) [24].

In terms of performance, PCM memories can be compared to Dynamic Random Access Memories (DRAM) and SRAM. When compared to S/DRAM, PCMs feature much slower latency with writing speeds typically above the  $100\text{ns}$  and a limited endurance in the  $10^6\text{-}10^9$  range [9]. PCMs also feature a higher write energy than other technologies including magnetic Hard Disk

Drives (HDDs) and NAND Flash [24]. Reductions in write latency and energy consumption are active areas of research, and while individual devices have been shown to achieve fast  $25\text{ns}$  cycles with an endurance up to  $10^{12}$ , low  $10\mu\text{A}$  RESET current and 10 year data retention [22], arrays of PCMs still need to catch up.

### 2.2.3 Ferroelectric Field Effect Transistor (FeFET)

Research on ferroelectric materials used for modulating the conductivity of a semiconductor began in Bell Labs in 1957 [28]. In 1974 the first Metal–Ferroelectric–Semiconductor (MFS) transistor was presented using bismuth titanate ( $\text{Bi}_4\text{Ti}_3\text{O}_{12}$ ) deposited on silicon [29]. However, the development of suitable devices was hindered by the lack of scalable ferromagnetic dielectrics, gate leakage, low data retention, and demanding integration [9],[28]. Other technologies with similar structures such as the floating-gate transistor saw much greater adoption. Finally, in 2011, evidence for ferroelectric properties in  $\text{SiO}_2$  (silicon oxide) doped  $\text{HfO}_2$  was discovered [30], leading to the development of promising scalable FeFET devices. In 2016, one-transistor (1T) FeFET-based eNVM arrays in NOR and AND configurations were demonstrated in a  $28\text{nm}$  HKMG process, showing data retention up to  $250^\circ\text{C}$  with an endurance of  $10^5$ . Later, in 2017, a 32 Mbit FeFET eNVM was reported with  $10\text{ns}$  switching speed,  $10^5$  cycle endurance, and data retention up to  $300^\circ\text{C}$  [31]. Applications for FeFETs also include neuromorphic computing [28], and IMC circuits, particularly NV-CAMs [32], [33].

The simplest FeFET structure is the Metal–Ferroelectric–Semiconductor (MFS), in which a layer of ferroelectric material is deposited over the transistor channel. However, due to integration drawbacks, a buffer layer was added leading to the preferred Metal–Ferroelectric–Insulator–Semiconductor (MFIS) structure. Fig. 2.1 (c) shows the structure of an MFIS FeFET cell. The ferroelectric layer (FE) is used to store information in the form of two equivalent polarization states  $P^-$  and  $P^+$ , which remain stable even when no electric field is being applied. The states are associated with the presence of permanent dipoles within the cell [28]. The interfacial layer (IL) is used to separate the FE and the transistor channel. The main functions of this layer include preventing the

diffusion of elements between the FE layer and the substrate, enabling deposition and growth of the FE layer, and providing a good channel-interface to maintain high transistor performance [28].

To switch between polarization states, a field larger than the coercive electric field (EC) is applied to the cell. The polarized FE layer induces a field in the FET channel due to the polarization charge, resulting in a change in threshold voltage ( $v_{th}$ ). For an n-channel device, when polarization points downwards, minority carriers are attracted to the channel increasing conductivity and causing a low threshold voltage (Erased state). Meanwhile, if polarization is pointing upwards, minority carriers are repelled and a high threshold voltage appears (Programmed state). The threshold difference between the erased and programmed state is known as the Memory Window (MW). Similar to PCMs, FeFETs programmed/erased using incremental pulses have been shown to achieve discrete, intermediate threshold voltage levels enabling MLC capabilities [34].

In terms of performance,  $\text{HfO}_2$  cells show great scalability, but suffer from a limited endurance in the  $10^4$  to  $10^5$  range [9]. Data retention problems occur due to the presence of a depolarization field caused by the non FE layers of the device [28]. To mitigate this field, high EC values are preferred, but these lead to a faster degradation of the IL layer from repeated program and erase cycles. Preventing IL degradation without affecting data retention is a current area of research [35].

#### 2.2.4 Magneric Random Access Memories (MRAM)

MRAM devices are one of the most promising NVM technologies offering a better performance in switching speed, write energy, data retention, and endurance compared to the other technologies discussed in this section [8]. Spin Transfer Torque MRAM (STTMRAM) devices in particular feature sub  $10\text{ns}$  writing speeds with above  $10^{12}$  cycling endurance [9], sparking interest in research for applications such as cache memories [36], neural networks [37], hardware accelerators [8], and cryptography [38], amongst others. Industry-led research has shown high-density integration architectures like the DMTJ crossbar array presented by Samsung in 2022 [39]. Additionally, STT-based

devices have been successfully commercialized by Everspin [40], selling STT-based DDR products for data-centers. Intel [41], and Global Foundries [42] have also began to release STT-MRAM products with a focus on IoT.

MRAMs are based on spintronics, which refers to technologies that use the spin of electrons and its associated magnetic moment as state variables in devices [43]. The basic unit device of MRAM is the Magnetic Tunnel Junction (MTJ).

### Single-Barrier Magnetic Tunnel Junctions (SMTJ)

The MTJ, or single-barrier MTJ (SMTJ), is a multilayer nano-pillar structure consisting of a stack of two ferromagnetic (FM) layers separated by a non-magnetic layer as shown in Fig. 2.1 (d). The insulating layer works to magnetically decouple the ferromagnetic layers, and must be thin to allow electrons to tunnel through the barrier when a sufficient voltage is applied. Magnetic anisotropy determines the directional dependence of the magnetic material. If the FM layers are aligned in parallel to the insulating layer the device is an in-plane MTJ (iMTJ), otherwise; the alignment is perpendicular (pMTJ). pMTJs (Fig. 2.1 (d)) have a lower switching current and more reliable switching [44].

The operating principles of an SMTJ cell are as follows. One of the FM layers, called the Pinned Layer (PL) has a fixed magnetic orientation. The other FM, called the Free Layer (FL), is able to switch between a parallel (P) and anti-parallel (AP) state with respect to the PL. When the layers are in P configuration the SMTJ shows a low resistance value, i.e.,  $R_P$ ; otherwise, if the layers are anti-parallel, the device has a higher resistance, i.e.,  $R_{AP}$ . The change in resistance is explained by the majority and minority spins of each layer. If both layers are parallel, electrons with majority spin in one FM layer can tunnel easily to the majority states of the other layer, while in the AP case majority and minority spins from one layer tunnel to fill minority and majority states of the other [43]. The key performance indicator is called the Tunnel MagnetoResistance (TMR), defined as

$$TMR = \frac{R_{AP} - R_P}{R_P} \quad (2.1)$$

In 1975, the first device with a TMR of 14% was reported using a Fe/Ge/Fe

structure [43]. Current devices use CoFeB ferromagnetic layers separated by a magnesium oxide (MgO) insulating layer. Commonly TMR values are in the 100% to 250% range, like Samsung's [45] integrated STT-MRAM arrays in 28nm fully-depleted silicon-on-insulator (FDSOI) processes which can achieve TMR values of 220%. The highest-to-date room temperature TMR is 604% [43].

The magnetic orientation of the free layer can be switched using different mechanisms. The first method is Field Induced Magnetic Switching (FIMS), where a current passing through orthogonal write lines produces an external field that would switch the SMTJ from P to AP and vice-versa. FIMS brought several drawbacks such as half-selectivity problems, high power consumption ( $I_{write} \geq 10mA$ ), and low density [43]. In 2004, Spin Transfer Torque (STT) was demonstrated experimentally for the first time [44]. Writing in STT devices is done by applying a bidirectional current through the junction. According to the direction of the current, flowing electrons are spin-polarized by the pinned layer, and their momentum is transferred to electrons in the free layer. The torque generated by this interaction can change the magnetic orientation of the free layer if it is strong enough, which occurs when a critical current  $I_{C0}$  is applied to the SMTJ.

The main challenge for STT-MTJs is the reduction of the critical current to improve switching energy and speed. Additionally, exposition to high voltages for long write pulses significantly degrades endurance [46]. The STT is larger when the magnetic moments are near anti-parallel than near parallel [44], resulting in an asymmetric value for the critical switching current. To reduce the critical switching currents, an additional PL is included in the MTJ stack. This device is introduced hereafter.

### **Double-Barrier Magnetic Tunnel Junction (DMTJ)**

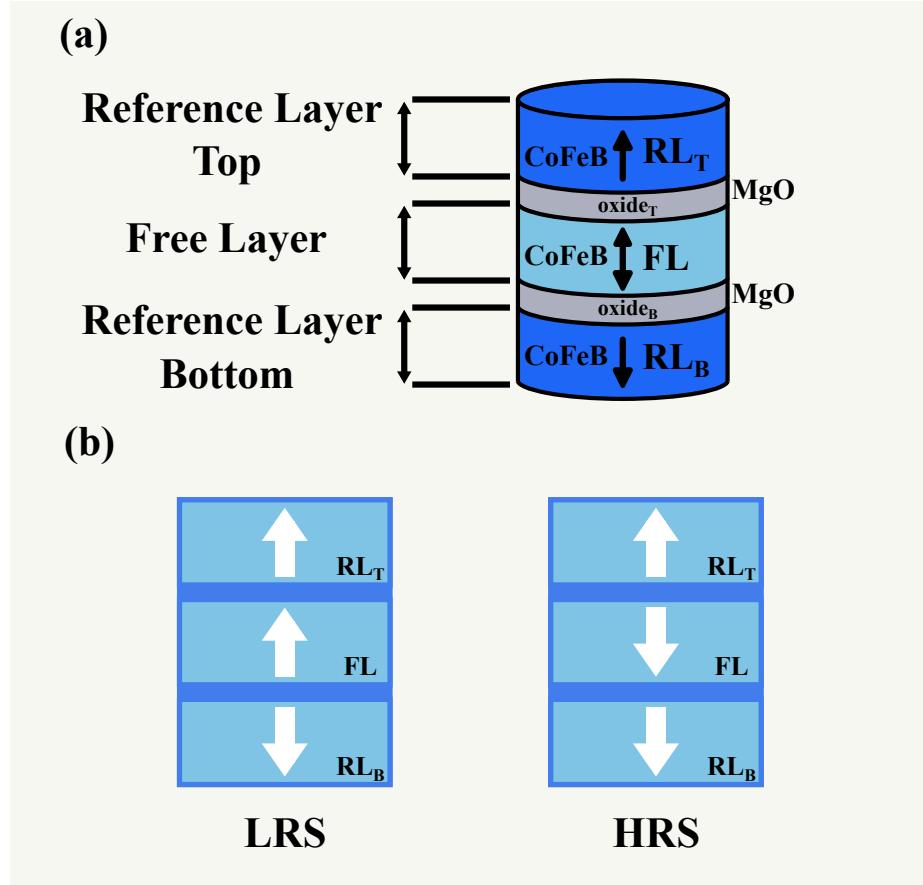

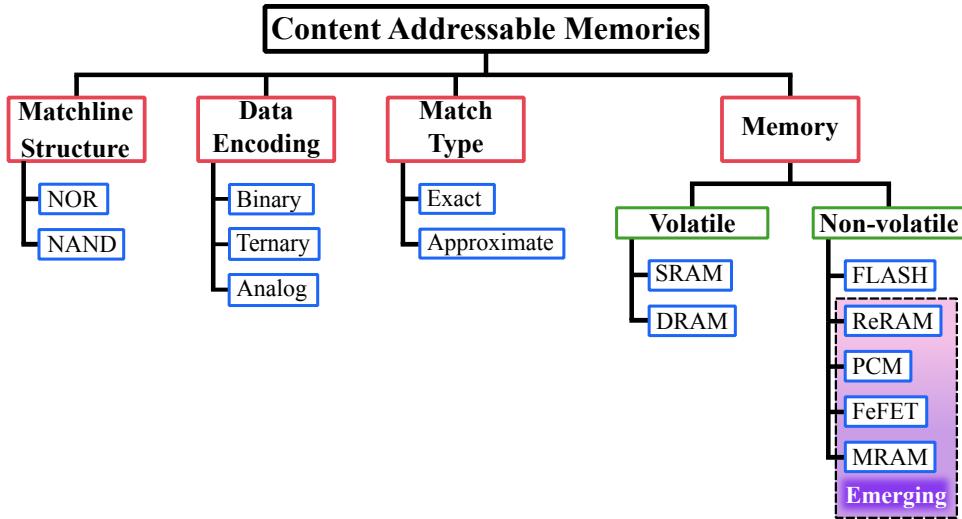

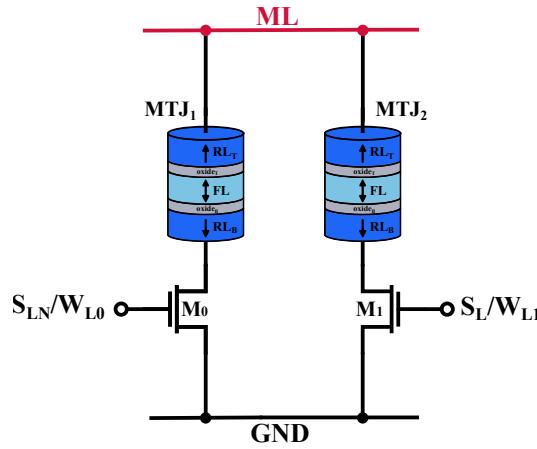

The Double Barrier Magnetic Tunnel Junction (DMTJ) structure increases the switching efficiency of the STT mechanism by introducing a second pinned layer as shown in Fig. 2.2. The three FM layers are separated by two thin oxide layers  $oxide_T$  (Top) and  $oxide_B$  (Bottom). The bottom layer (PLb) has a magnetic orientation antiparallel to the top layer (PLt) resulting in one

Figure 2.2: Double Barrier Magnetic Tunnel Junction (DMTJ). (a) Device structure. (b) Device states.

junction always being in AP state, reducing the total TMR of the device. In exchange, the critical switching current  $I_{C0}$  is reduced up to a factor of 10 [44], and becomes equal for both  $P \rightarrow AP$  and  $AP \rightarrow P$  transitions.

Finally, STT methods introduce a stochastic nature to DMTJ/SMTJ switching. Initially, when a write current is just applied, the magnetic orientations of all layers (PLt, PLb, FL for DMTJs) are collinear, and the resulting torque is zero. For STT to take effect, a miss alignment caused by thermal fluctuations is required, which introduces a random wait time before switching [43]. Therefore, to ensure a low Write Error Rate (WER), the write current must be applied for a longer time than the ideal device switching time. Additionally, as DMTJs (thus  $I_{C0}$ ) scale down, using the same current path during the write

and read operations increases the risk of overwriting stored data. For these reasons, alternative switching mechanisms for both SMTJs and DMTJs are being studied. Notable candidates are Spin-Orbit Torque (SOT) and Voltage Controlled Magnetic Anisotropy (VCMA) [8].

## 2.3 Organization of the Thesis

This thesis studies the use of STT-MRAM devices in designing Non-Volatile CAMs for IMC architectures that feature a high frequency of search and update operations. The rest of this work is organized as follows: Chapter 3 presents the required background to understand the principles of Non-Volatile CAMs (NV-CAMs). Chapter 4 presents the principles and evaluation of a high-performance, reliable STT-MRAM based NV-CAM design. Chapter 5 presents a comparative performance analysis with other STT-MRAM based cells found in the literature. Finally, Chapter 6 summarizes the thesis and presents the research output of this work.

# Chapter 3

## Background

### 3.1 Content Addressable Memories

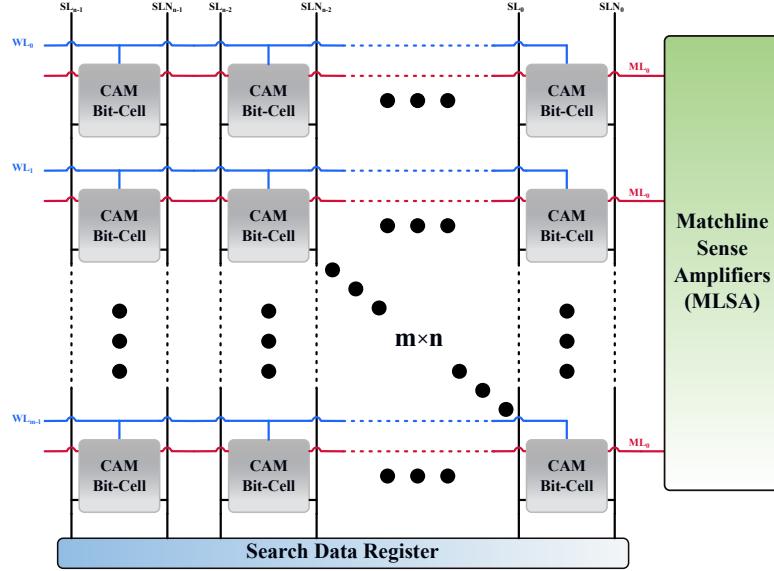

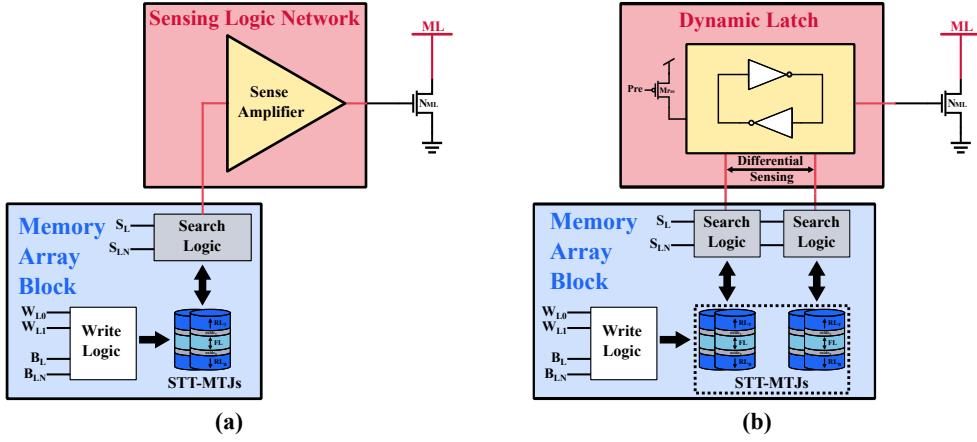

Fig. 3.1 shows the block diagram of the CAM architecture. The memory array consists of  $m \times n$  CAM bit cells arranged in  $m$  words of length  $n$ . Each word is connected to a word-line  $WL_j$  and a matchline  $ML_j$ . Search-lines  $SL_i$  and  $SLN_i$  run vertically through each column  $n$ . The write operation is controlled by the WLs, and data is loaded through the bit-lines (not shown). For the search operation, the word in the Search data Register is loaded into the search-lines. The outputs on the matchlines are sensed by the Matchline Sense Amplifiers (MLSA) to determine whether the result is a match or mismatch. The number of bits in a CAM word is usually in the range of 36 to 144 bits [5].

Fig. 3.2 shows an overview of the classification of CAMs based on the matchline type, data encoding, match type, and memory type. There are two types of matchline structures in CAMs: NOR and NAND matchlines. NOR matchlines feature a high search speed, at the cost of increased energy consumption. NAND matchlines feature a more energy-efficient search but suffer from low noise margins, and a quadratic increase in delay for every extra cell in the CAM word [5].

CAM cells can be designed to store different types of data. Binary CAMs (BCAMs) consist of arrays of cells made with a single memory device (e.g., one SRAM cell, or one ReRAM), and can store and match against words containing only '1's and '0's. Ternary CAMs (TCAMs), are able to store an additional

Figure 3.1: Content Addressable Memory (CAM) block diagram.

value, i.e., 'X'. This value acts as a *don't care*, that matches against both a '0' and a '1'. This feature increases data density, and enables searches with partial matches, which are heavily featured in applications like packet forwarding in network routers [5]. TCAM cells require two bits (memory devices) per cell to store the extra state. In cases where a TCAM is needed, but unavailable, BCAMs can be repurposed by using two cells to encode each symbol at the cost of halving the original capacity [47]. Analog CAMs (ACAMs) use the programmable analog characteristics of emergent memory devices to compare an analog search query with analog ranges encoded in the CAM cells [48]. Some ACAMs can be used as memory-dense replacements for digital CAMs by storing narrow ranges as discrete levels [4].

In conventional CAMs, the search operation is designed such that a match occurs only when the search query word and the stored data entries are identical (except for *don't care* bits), otherwise; the operation results in a mismatch. Approximate CAMs allow a certain number of mismatch bits to appear between the search query word, and stored data, leveraging the highly parallel, fast operation of CAMs to enable applications requiring approximate search, like pattern recognition, DNA sequencing, and machine learning amongst others [49].

Figure 3.2: Content Addressable Memory taxonomy.

### 3.1.1 CMOS CAMs

CMOS-based CAMs use volatile SRAM cells for data storage for their fast and reliable search operation. This speed comes at the cost of increased energy consumption, and circuit area. Besides the dynamic energy dissipated by the matchlines and search-lines, the SRAM bit-cells show a high static energy consumption due to their large leakage current [50]. Emerging memory devices are being studied to propose alternative CAM designs featuring low standby power, no leakage, and high memory density [47]. In addition to the non-volatile nature of emergent devices, energy and area-efficient CAM systems enable new potential application spaces which are detailed in Section 3.2.

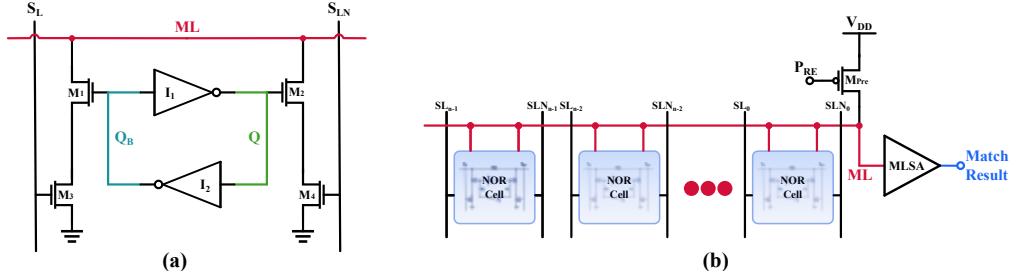

The conventional CMOS CAM cell uses the 6T-SRAM that holds one of two stable states formed by the feedback loop of two cross-coupled inverters. Nodes  $Q$  and  $Q_B$  output the stored data, and extra transistors are added to the cell to enable data search. Fig. 3.3 (a) shows the circuit diagram for the 10T-NOR CAM cell, where the bit-lines and access transistors are omitted for clarity. Transistors  $M_1$  and  $M_3$  are driven by the data stored in  $Q_B$ , and the search bit loaded to  $S_L$ , respectively. The pair forms a discharge path for the matchline that is disabled when either transistor is turned off. Likewise, transistors  $M_2$  and  $M_4$  form a second discharge path controlled by the voltage in  $Q$ , and  $S_{LN}$ . In case of a match, both discharge paths are disabled since the voltages in  $Q_B$ ,

$S_L$  and  $Q$ ,  $S_{LN}$  are complementary. For instance, the search '0' operation sets  $S_L = 0$  and  $S_{LN} = V_{DD}$ , and a stored '0' means that  $Q_B = V_{DD}$  and  $Q = 0$ , turning off transistors  $M_2$  and  $M_3$ . On the other hand, if the stored value was a '1',  $Q = 1$ , the discharge path through  $M_2$  and  $M_4$  is enabled. Thus, a mismatch ensures that the matchline is connected to ground through one of the two discharge paths. NOR-type cells are connected in parallel to the matchline to form a CAM word as shown in Fig.3.3 (b).

Figure 3.3: (a) 10T-NOR CAM cell. (b) NOR matchline with cells connected in parallel.

The operation of the NOR matchline requires three phases. In the first phase, the search-lines are driven to  $S_L = S_{LN} = 0$ , to ensure that all discharge paths are disconnected. During the second phase,  $PRE$  is driven low, and the matchline is pre-charged to  $V_{DD}$  through transistor  $M_{Pre}$ . Finally, during the evaluation phase,  $PRE = V_{DD}$ , and the search-lines are driven according to the search word. In the case of a match, all discharge paths are disabled and the matchline voltage remains high. Conversely, if there is a mismatch, there is at least one active path to ground which discharges the matchline. The sense amplifier senses the matchline, and outputs a value of  $V_{DD}$ , or 0 indicating a match or mismatch, respectively.

Fig. 3.4 (a) shows the circuit diagram for the 9T-NAND CAM cell, with the bit-lines and access transistors omitted for clarity. Transistors  $M_2$  and  $M_3$  act as pass transistors connecting  $S_L$  and  $S_{LN}$ , respectively, to the gate of transistor  $M_1$ . According to the data stored in nodes  $Q$  and  $Q_B$ , the gate of  $M_1$  is going to be driven by  $S_{LN}$  if the cell stores a '0', and  $S_L$  is the cell stores a '1'. If the search is a match, the voltage at the gate of  $M_1$  will be  $V_{DD} - v_{th}$ , turning the transistor on, and connecting the segment  $ML'_i$  to  $ML'_{i+1}$ . For

instance, searching for a '1' ( $S_L = V_{DD}$ ,  $S_{LN} = 0$ ), in a cell storing a '1' ( $Q = V_{DD}$ ), will drive the gate of  $M_1$  high through pass transistor  $M_2$ . In the case that the cell was storing a '0', the gate of  $M_1$  receives a 0 from  $S_{LB}$  through pass transistor  $M_4$ . Thus, a mismatch turns off the transistor  $M_1$  and disconnects the matchline. NAND-type cells are connected in series to form a CAM word as shown in Fig. 3.4 (b).

Figure 3.4: (a) 9T-NAND CAM cell. (b) NAND matchline with cells connected in series.

The NAND matchline requires two phases. During the pre-charge phase, the voltage of *eval* is driven low to disconnect the matchline from ground via transistor  $M_E$ . At the same time  $PRE = 0$ , charging the matchline through transistor  $M_{Pre}$ . During the evaluation phase, both  $PRE$  and *eval* are risen to  $V_{DD}$ , and the search-lines are driven according to the search word. In case of a match, a path is created connecting the matchline to ground through all the NAND cells, causing it to discharge. In the case of a mismatch, the path is disconnected by at least one cell, and the matchline voltage stays close to  $V_{DD}$ . The MLSA outputs a value of 0 or  $V_{DD}$  indicating a match, or mismatch respectively.

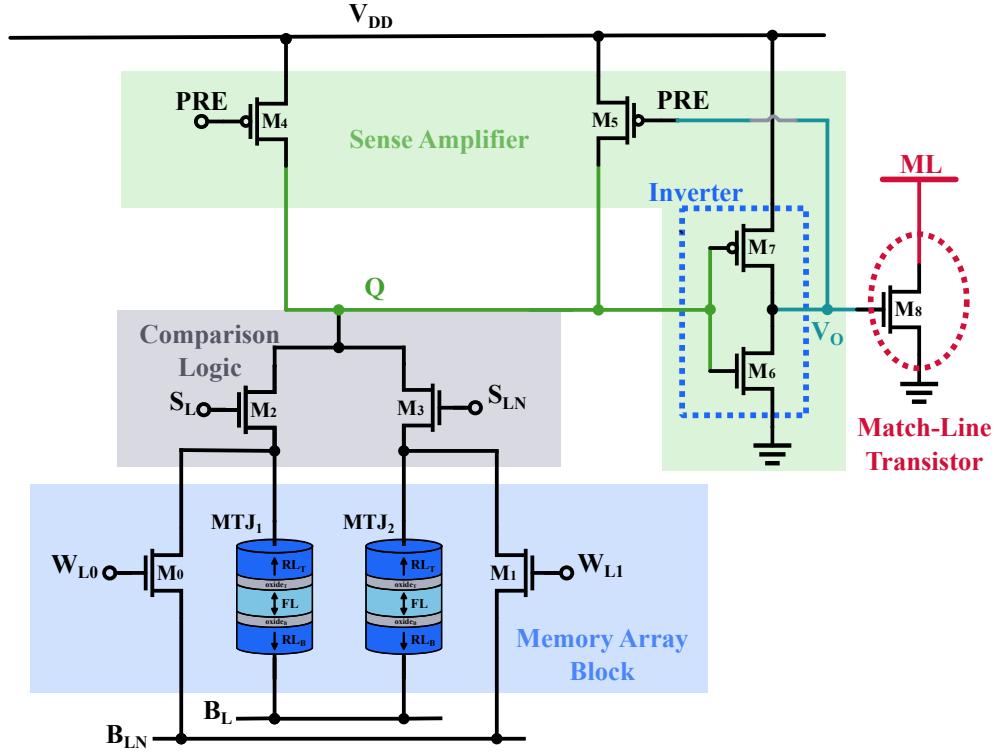

### 3.1.2 Non-Volatile CAMs Based on STT-MRAM Technology

Non-volatile CAMs based on STT-MRAM technology mainly offer compact area footprint, negligible leakage power consumption and scalability. The high switching speed of MRAM devices translates into low-latency write operations. Fig. 3.5 shows the structure of the 2T2MTJ cell presented in [51], featuring

one of the simplest NV-CAM cell structures. The cell stores bit information in the resistance states of the MTJ devices. During search operations, one of the two paths is enabled, and the matchline discharges at a rate that depends on the device resistance. The difference in resistance between HRS and LRS is measured by the TMR, and determines the sensing margin and reliability of the 2T2MTJ cell. This design features a very low area footprint but must operate in a word-parallel, bit-serial, manner to avoid search errors. This results in a long search latency and increased energy consumption [47].

Figure 3.5: Circuit diagram for the 2T2MTJ NV-CAM cell [51].

The low TMR in STT-MTJ devices becomes a significant design challenge. As a result, all STT-MRAM-based NV-CAM cell designs suffer from reliability considerations due to process variations, leading to search errors. The Search Error Rate (SER) is a key parameter in the performance of a NV-CAM/TCAM, limiting word length and possible applications.

To achieve fast, reliable, and energy-efficient search operations, more recent STT-MRAM bit-cell designs include more complex transistor networks. The two main architectures for such networks are discussed below.

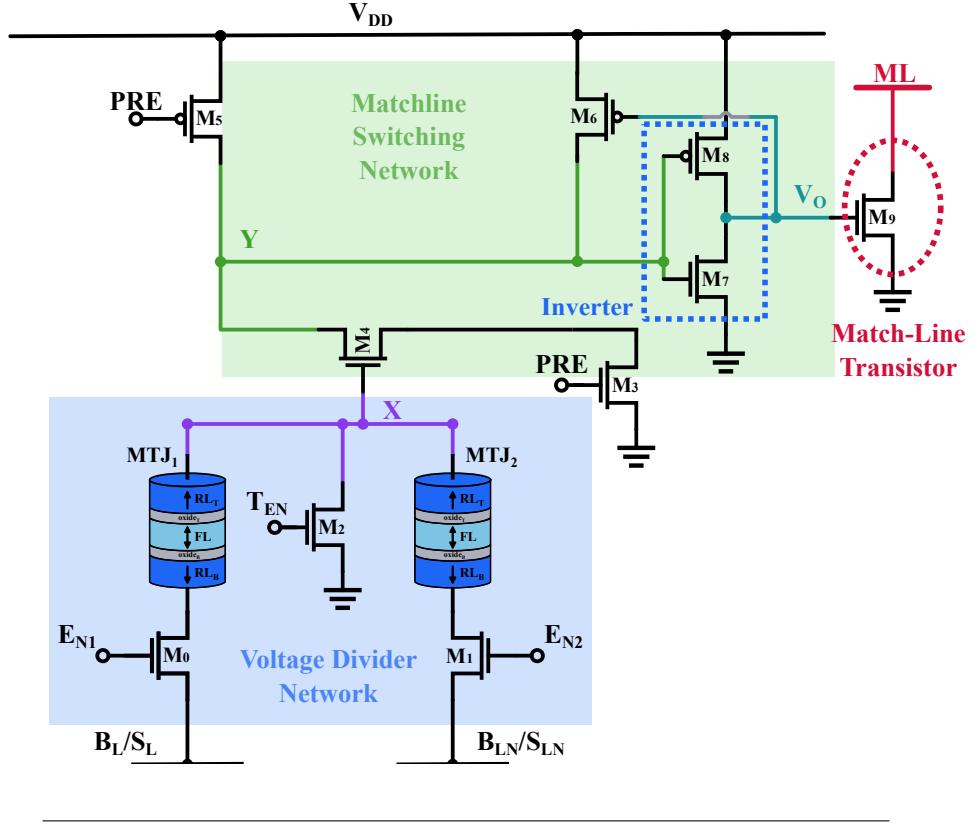

### Voltage Divider Structures

Fig 3.6 (a) shows the basic structure of voltage-divider cells. Voltage divider solutions feature a moderate number of transistors, and usually no more than two MTJ devices. The sensing logic network is used to amplify the voltage

Figure 3.6: Top level diagram for the most common type of STT–MRAM based NV–CAMs explored in literature. (a) Voltage divider structure. (b) Latch-based structure.

difference at the output of the memory array block, and drive the matchline transistor.

Voltage divider cells tend to suffer from higher SER and longer search times leading to more energy consumption. While some designs rely on static sensing logic [52], [53], other voltage-divider based solutions [54], [55], use dynamic-based buffers in the sensing network to provide a faster and more reliable response.

### Latch Based Structures

Fig 3.6 (b) shows the basic structure of latch-based type cells. This type of cell uses a greater amount of transistors and MTJs to implement a dynamic, differential sensing scheme, which serves to amplify the small voltage difference produced by the memory array block in order to drive the matchline transistor. Latch-based cells suffer from a higher area footprint, but provide a faster, more reliable search operation [56], [50].

## 3.2 Non-Volatile CAMs Application Space

NV-CAMs share the same capabilities as traditional CAMs, which have been studied for a wide variety of applications including parametric curve extraction,

image encoding/decoding, and data compression. Relevant literature for the aforementioned applications is cited in [5]. The most common use for CAMs is packet classification and forwarding in network routers [57]. Routers must forward data packets to the correct output based on addresses that are stored as entries in routing tables. As the sizes of the table and the entries grow, TCAMs become a candidate to handle the demand for ever-growing networking speeds [47].

The introduction of novel devices in CAMs, accompanied by improvements in circuit and architecture design have opened the gates to new, emerging applications. A review of emergent applications like neuromorphic associative memory, text mining, pattern recognition in wearable electronics, and reconfigurable computing, among others, can be found in [47]. Reconfigurable computing systems like Field Programmable Gate Arrays (FPGAs) rely on lookup tables and configurable interconnect frameworks. Large CAMs configured as programmable logic arrays (PLAs) can lower memory requirements when mapping certain functions, while reducing the overhead of the programmable interconnect network [58].

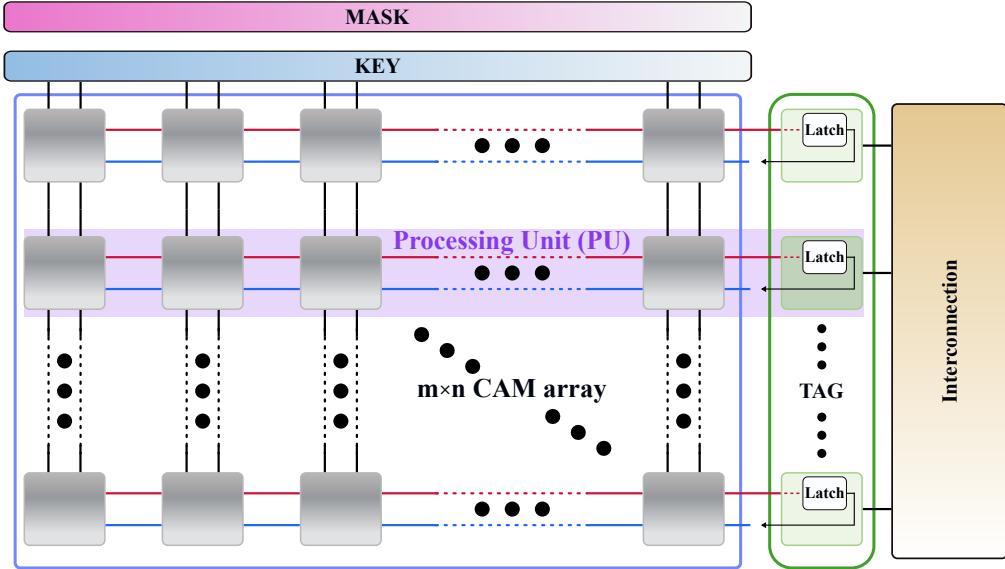

The remainder of this section focuses on Associative Computing Systems (ACS), particularly Associative Processors (AP). An AP is a non-Von Neumann in-memory computing architecture that performs single instructions in parallel across multiple data entries within a CAM memory array [6].

Fig. 3.7 shows the architecture of an associative processor. The main component of the AP is the  $m \times n$  cell CAM array that is used to store and process data. The CAM search query is stored in the KEY register, while the MASK register is used to define which columns are “active”, meaning that they are affected by the AP write (update) and search operations. Each CAM row is connected to a TAG, forming a Processing Unit (PU). The TAG register is used to mark the rows that match during search operations. The interconnection block is a switching matrix that enables PUs to communicate in parallel with each other [59]. Some AP architectures may also feature a reduction tree connected to the TAGs, which enables the quick accumulation of TAG bits that are useful for vector to scalar transformations [15].

The execution principle of an AP is based on a succession of search and up-

Figure 3.7: Associative Processor (AP) Architecture. Every CAM row is connected to a TAG, forming a Processing Unit.

date phases. During the search phase, the KEY is compared in parallel to every stored entry. During the update phase, data is written into the columns specified in MASK for every row that matched in the search phase. Any single-instruction–multiple–data (SIMD) function  $f(x)$ , is transformed into a lookup table which acts as a truth table [59]. The AP evaluates the LUT in order by searching for the table input patterns and updating matching words with the corresponding table output. Operations are performed in a bit serial, word parallel manner, for more efficient LUT implementations [15]. The number of cycles is determined by the size of the argument  $x$ , regardless of the size of the dataset.

The associative processing execution model is limited by the throughput of single pattern searches in large, complex calculations, and the high write frequency of the search and update operations [6]. To mitigate those issues, novel AP architectures and data encoding methods have been explored in literature. For instance, the “Hyper-AP” design presented in [60] introduces multi-pattern search, and multi-search write computations in order to reduce the number of read and write operations. New circuit structures paired with novel architectures, and the improved performance of emergent devices have

inspired a renewed interest in associative processors [55].

Finally, STT–MRAM-based NV-CAMs have been studied as a suitable candidate for AP designs targeting problem sets that benefit from associative computing hardware. For example, the low power AP developed in [61] was fabricated with a  $90nm$  CMOS/MTJ hybrid technology, and has been analyzed for image pattern recognition applications, consuming  $600\mu W$  of operating power at a frequency of  $20MHz$ . Additionally, the “AM<sup>4</sup>” AP presented in [3] builds upon the MRAM crossbar array structure presented introduced in [39], and has been analyzed for genome sequencing alignment workloads.

# Chapter 4

## Non-Volatile Content-Addressable Memory (NV-CAM) Design

This chapter studies the hybrid CMOS/MTJ design and performance evaluation of the proposed 17-transistor 4 (Double-Barrier) MTJ cell. This design builds upon the cell presented in [56]. Two extra transistors are added to enable fast and reliable write operations, which are crucial when targeting applications involving frequent entry updates such as Associative Processors. By adding the DMTJ technology and extra circuitry, the proposed cell achieves good performance while maintaining the reliability of the original design. The design presents standard-sized transistors. The 17T4MTJ cell is designed in TSMC 65nm technology using the Cadence Virtuoso software suite. The DMTJ devices are simulated using the Verilog-A compact model described below.

### 4.0.1 Overview of the MTJ Compact Model

The design of the non-volatile CAM cells uses DMTJs devices simulated using the Verilog-A compact model developed in [62]. The model exploits physics-based analytical formulas to calculate the resistance and statistical switching characteristics for

CoFeB/MgO/CoFeB/MgO/CoFeB perpendicular STT-DMTJs. The simulated switching time distributions are comparable to full micromagnetic and

experimental results [62]. Finally, the model considers Gaussian process variations for the thickness of both  $oxide_T$  and  $oxide_B$ , the thickness of the free layer, cross-sectional area, and TMR.

Table 4.1 reports the main physical device parameters. Detailed calibration of the device is based on the parameters reported in [63], which were chosen to match experimental data for SMTJs. The DMTJ has a diameter of  $20nm$ , a free layer thickness of  $1.2nm$ , a top oxide thickness of  $850pm$ , and a bottom oxide thickness of  $400pm$ . The critical switching current is  $6.182\mu A$ , and the resistance for both states at  $V_{DC} = 0V$  are  $42.8k\Omega$  for the high resistive state, and  $18.34k\Omega$  for the low resistive state. This results in a TMR of about 140%.

Table 4.1: DMTJ device parameters

| Parameter                            | Unit      | Value |

|--------------------------------------|-----------|-------|

| Diameter (d)                         | nm        | 20    |

| FL thickness ( $t_{FL}$ )            | nm        | 1.2   |

| Top oxide thickness ( $t_{oxT}$ )    | pm        | 850   |

| Bottom oxide thickness ( $t_{oxB}$ ) | pm        | 400   |

| Critical current $I_{CO}$            | $\mu A$   | 6.182 |

| HRS (at 0V)                          | $k\Omega$ | 42.84 |

| LRS (at 0V)                          | $k\Omega$ | 18.34 |

| TMR (at 0V)                          | %         | 140%  |

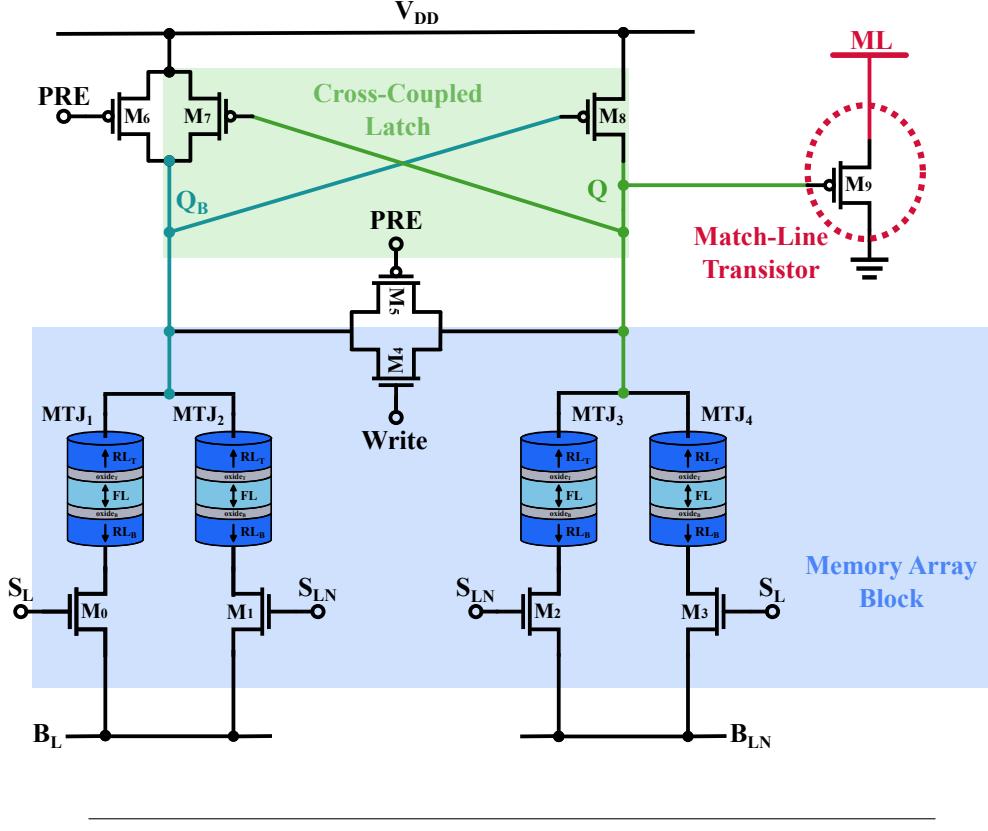

## 4.1 17T4MTJ Cell Structure

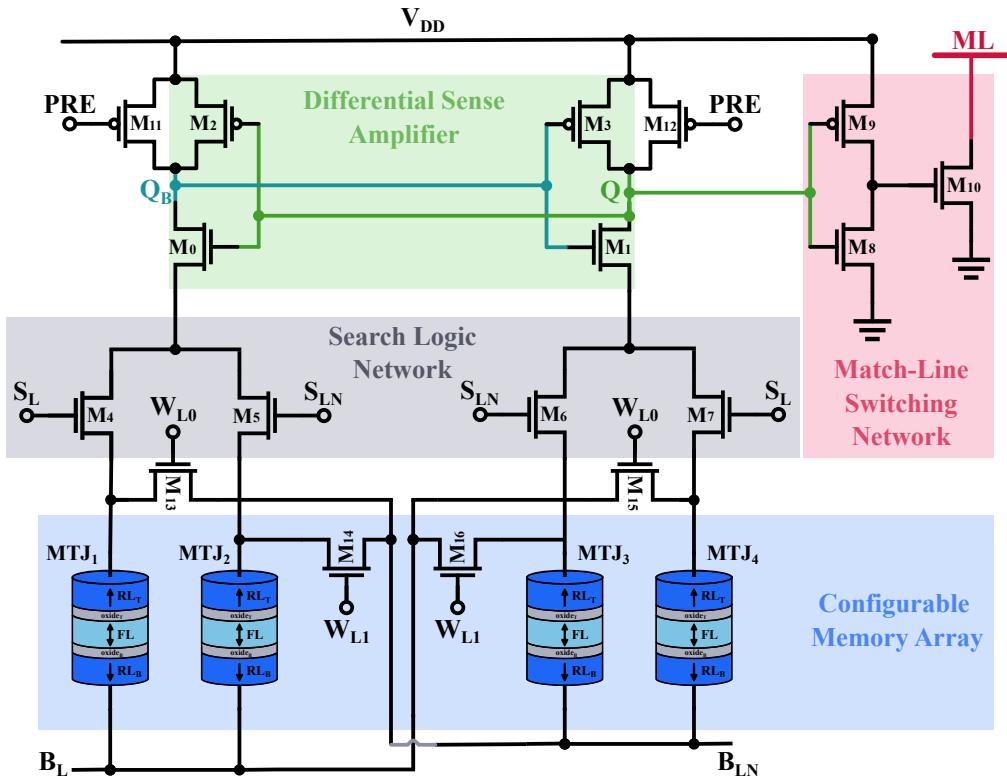

Fig. 4.1 shows the schematic diagram for the proposed cell. The design consists of 17 transistors and 4 DMTJs (17T4MTJ) and can be divided into several blocks. First is the Memory Array Block (MAB) which is formed by the DMTJs  $MTJ_{1-4}$ , and transistors  $M_{13}, M_{14}, M_{15}, M_{16}$ . Compared to the MAB presented in [56], the block was modified to give each MRAM device its access transistor for faster writing. The MAB stores non-volatile data according to the resistance of each device as shown in Table. 4.2. Although the MAB can be used to store a ternary value 'X', this, and subsequent chapters only consider the cell for binary data search.

Next is the Search Logic Network (SN), consisting of transistors  $M_4, M_5$ ,

Table 4.2: Memory array block data encoding

| Stored Data | Device State |         |         |         |

|-------------|--------------|---------|---------|---------|

|             | $MTJ_1$      | $MTJ_2$ | $MTJ_3$ | $MTJ_4$ |

| '0'         | HRS          | LRS     | HRS     | LRS     |

| '1'         | LRS          | HRS     | HRS     | LRS     |

| 'X'         | LRS          | LRS     | HRS     | HRS     |

$M_6, M_7$  which handles the search input, enabling and disabling access to the MAB. Then, the Differential Sense Amplifier (DSA) consisting of two cross-coupled inverters (latch) made up from transistors  $M_0, M_2$  and  $M_1, M_3$ , as well as precharge transistors  $M_{11}$  and  $M_{12}$ . Finally, the Match-Line Sensing Network (MLS) is driven by the output of the latch-based DSA and consists of an inverter  $M_8, M_9$  and the match-line transistor  $M_{10}$ .

Figure 4.1: Circuit diagram for the proposed 17T4MTJ NV-CAM cell.

## 4.2 Cell Operation

This section gives a detailed analysis of the write and search cell operations.

### 4.2.1 Write Operation

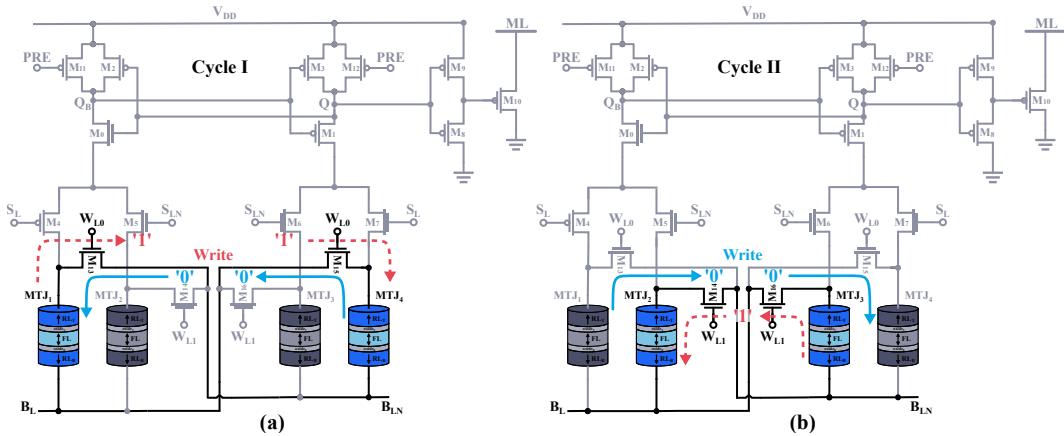

During the write operation, the search-lines  $S_L$  and  $S_{LN}$  are driven to ground ( $V_{SL/SLN} = 0V$ ), turning off the search logic network transistors and disconnecting the sense amplifier from the memory array. The operation involves only the MAB and is divided into two phases. During phase I, the bit-line ( $B_L, B_{LN}$ ) voltage is set, and transistors  $M_{13}, M_{15}$  are enabled by the word-lines, allowing a bidirectional current flow from the bit-lines through  $MTJ_1$  and  $MTJ_4$  as shown in Fig. 4.2 (a). During phase II, the voltage difference between  $B_L$  and  $B_{LN}$  is reversed and transistors  $M_{14}, M_{16}$  are enabled as shown in Fig. 4.2 (b). The current is now able to flow through the two internal DMTJs  $MTJ_2, MTJ_3$ .

Figure 4.2: Write operation for the 17T4MTJ NV-CAM cell. (a) Phase 1 writes to  $MTJ_{1,4}$  (b) Phase 2 writes to  $MTJ_{2,3}$ .

The write operation is verified by transient simulations of the cell, which involve writing two data values '0' and '1'. The operation was performed out on a single 17T4MTJ cell initially storing a '1', meaning the starting states of the DMTJs are (LRS, HRS, LRS, HRS) for  $MTJ_{1-4}$ , respectively. The supply voltage was set as  $V_{DD} = 1V$ . The resulting waveforms are shown in Fig. 4.3. As expected, each write operation requires two cycles to complete. During the

Figure 4.3: Timing diagram for the write operation of the proposed 17T4MTJ NV-CAM cell.

first cycle, corresponding to phase I,  $W_{L0}$  is set to  $V_{DD}$  while  $W_{L1}$  is set to 0, connecting the outermost devices,  $MTJ_1$  and  $MTJ_4$  to the write path. When writing a '0', the bit-lines are set as  $B_L = 0$  and  $B_{LN} = V_{DD}$ , switching  $MTJ_1$  to HRS and  $MTJ_4$  to LRS. To write a '1', the bit-lines are set to the inverse values  $B_L = V_{DD}$  and  $B_{LN} = 0$ , switching  $MTJ_1$  to LRS and  $MTJ_4$  to HRS. During the second cycle, corresponding to phase II,  $W_{L1}$  is set to  $V_{DD}$  and  $W_{L0}$  is set to 0, which connects the innermost devices,  $MTJ_2$  and  $MTJ_3$  to the write path. During this phase, the bit-lines are set to the opposite values of the previous phase. Therefore, for the case of a '0',  $B_L = V_{DD}$  and  $B_{LN} = 0$ , switching  $MTJ_2$  to LRS and  $MTJ_3$  to HRS. Otherwise, for a '1',  $B_L = 0$  and  $B_{LN} = V_{DD}$ , switching  $MTJ_2$  to HRS and  $MTJ_3$  to LRS.

Table. 4.3 summarizes the search-line, word-line, and bit-line input combinations for each write phase, as well as the stored states of each DMTJ. The

cycle time ensures that writes during each phase are carried out with a WER of  $10^{-7}$ .

Table 4.3: Write Operations for the proposed 17T4MTJ NV-CAM cell

|           |    | Signals    |          |          |          |          | States DMTJ <sub>1,2,3,4</sub> * |         | Cycle Time |

|-----------|----|------------|----------|----------|----------|----------|----------------------------------|---------|------------|

| Operation |    | $S_{L/LN}$ | $B_L$    | $B_{LN}$ | $W_{L0}$ | $W_{L1}$ | Initial                          | Final   |            |

| Write '0' | I  | 0          | 0        | $V_{DD}$ | $V_{DD}$ | 0        | L,H,L,H                          | H,H,L,L | $\sim 2ns$ |

|           | II | 0          | $V_{DD}$ | 0        | 0        | $V_{DD}$ | H,H,L,L                          | H,L,H,L |            |

| Write '1' | I  | 0          | $V_{DD}$ | 0        | $V_{DD}$ | 0        | H,L,H,L                          | L,L,H,H | $\sim 2ns$ |

|           | II | 0          | 0        | $V_{DD}$ | 0        | $V_{DD}$ | L,L,H,H                          | L,H,L,H |            |

\* HRS and LRS states are abbreviated as H and L.

#### 4.2.2 Search Operation

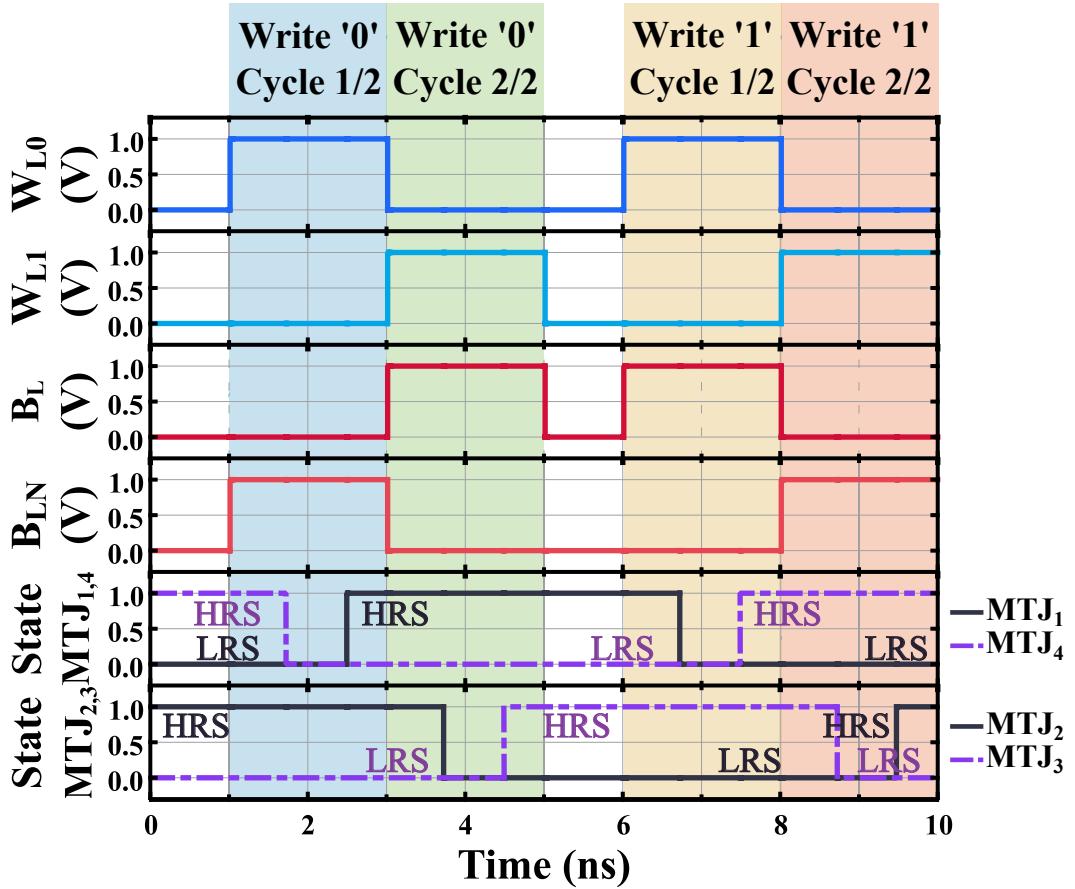

During the search operation, the bit-lines  $B_L$  and  $B_{LN}$  are grounded ( $V_{BL/BLN}$ ) to provide a discharge path for the dynamic latch. The operation is divided into two phases and involves all blocks in the circuit. The first phase is the pre-charge phase. As shown in Fig. 4.4 (a),  $S_L$  and  $S_{LN}$  are set to 0, disconnecting the lower blocks of the circuit. The  $PRE$  signal driven low, allowing transistors  $M_{11}$  and  $M_{12}$  to charge nodes  $Q$  and  $Q_B$  to  $V_{DD}$ , while turning off transistor  $M_{10}$  to avoid shorting the matchline to ground. The matchline is pre-charged to  $V_{DD}$  by a pass transistor external to the cell.

The second phase is the evaluation phase. During this phase, the  $PRE$  signal is driven to  $V_{DD}$ , the bit-lines are connected to ground, and the word-lines  $W_{L0}$  and  $W_{L1}$  are turned off to avoid bypassing the memory array block. The voltages on  $S_L$  and  $S_{LN}$  are set to enable the correct paths through the search logic network. Fig. 4.4 (b) illustrates the enabled discharge paths for a '0' search, which involve  $MTJ_2$  and  $MTJ_3$ . On the other hand, Fig. 4.4 (c) shows the enabled paths for a '1' search, involving  $MTJ_1$  and  $MTJ_4$ .

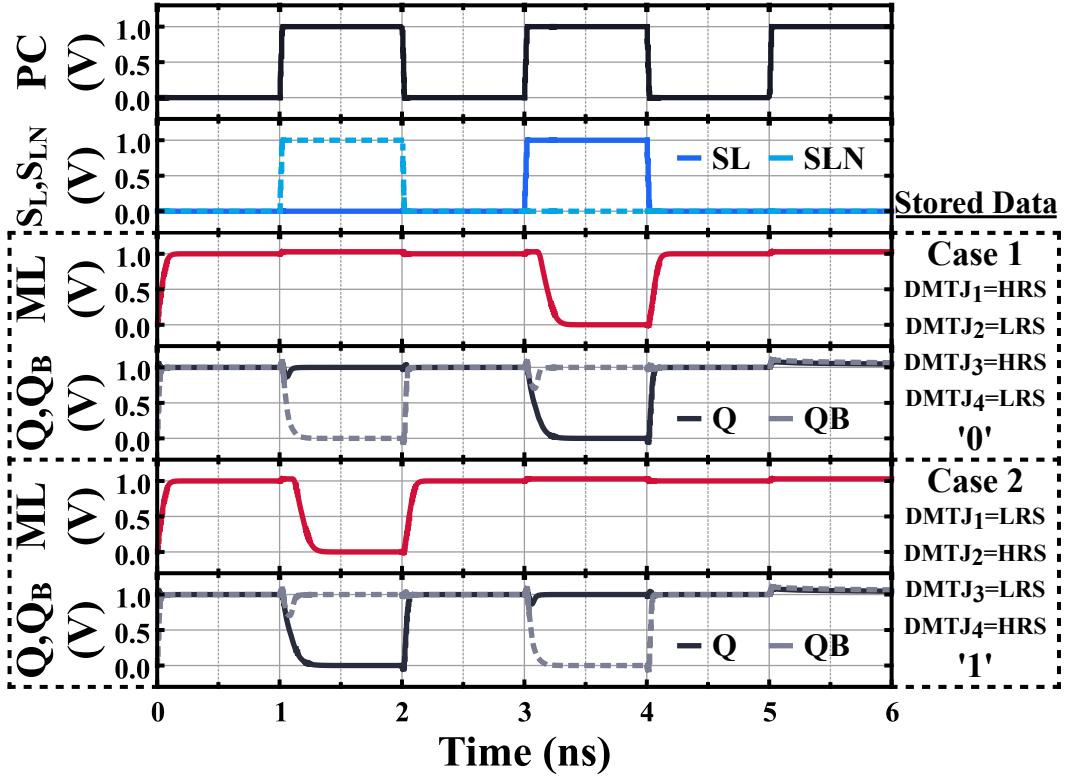

The search operation is verified by transient simulations that involve searching for '0', '1', and 'X' (don't care) values on a circuit containing a single 17T4MTJ bit-cell with a  $100fF$  load capacitance connected as a NOR-type matchline (ML). The ML is pre-charged by a pMOS transistor of width  $1\mu m$  and length  $60nm$ . The supply voltage used was  $V_{DD} = 1V$ . The resulting waveforms are

Figure 4.4: Search operation for the 17T4MTJ NV-CAM cell. (a) Pre-charge phase. (b) Evaluation phase for Search '0'. (c) Evaluation phase for Search '1'.

shown in Fig. 4.5.

The search requires two cycles to complete both phases. The search waveforms were simulated for two cases: in Case 1 the cell stores a '0' while in Case 2 the cell stores a '1'. During the pre-charge phase,  $PRE$ ,  $S_L$  and  $S_{LN}$  are set to 0, allowing, the  $ML$ , and nodes  $Q$  and  $Q_B$  to be driven to  $V_{DD}$ . The evaluation phase by setting the search-line voltages and raising  $PRE$  to  $V_{DD}$ .

For a search '0' operation  $S_L = 0$ ,  $S_{LN} = V_{DD}$ , and discharge paths through the innermost DMTJs are enabled. In the case of a stored '0' ( $MTJ_2 = LRS$ ,  $MTJ_3 = HRS$ ), the resistance through the path formed by  $M_0$ ,  $M_5$  and  $MTJ_2$  is lower than that through  $M_1$ ,  $M_6$  and  $MTJ_3$ , causing the node  $Q_B$  to discharge faster than  $Q$ . The voltage difference between the nodes is quickly amplified by the positive feedback of the cross-coupled inverters until  $Q_B$  reaches 0 and  $Q$  returns to  $V_{DD}$ . As a result, transistor  $M_2$  on the leftmost

Figure 4.5: Timing diagram for the search operation of the proposed 17T4MTJ NV-CAM cell. Search '0', '1', and 'X' are verified for both possible stored values.

path and transistor  $M_1$  on the rightmost path are turned off, meaning that after a short switching delay, no current flows through the DMTJs from  $V_{DD}$  to  $B_L$  or  $B_{LN}$ . The voltage at the input of transistor  $M_{10}$  is 0, so the transistor remains off and the matchline does not discharge, indicating a match. In case of a stored '1' ( $MTJ_2 = HRS$ ,  $MTJ_3 = LRS$ ), the path resistances are reversed, and node  $Q$  begins to discharge faster than node  $Q_B$ . The positive feedback of the latch amplifies this difference and drives  $Q_B$  to  $V_{DD}$  while  $Q$  fully discharges to 0. Transistors  $M_0$  and  $M_3$  are turned off, avoiding direct current paths from  $V_{DD}$  to  $B_L$  or  $B_{LN}$ . The voltage at the input of  $M_{10}$  is  $V_{DD}$ , creating a discharge path for the ML, indicating a mismatch.

Likewise, for a search '0' operation  $S_L = V_{DD}$ , and  $S_{LN} = 0$ , and discharge paths through the outermost DMTJs are enabled. In case of mismatch (stored '0'),  $MTJ_1 = HRS$  and  $MTJ_4 = LRS$ , causing node  $Q$  to discharge faster, eventually reaching '0' and driving the input of  $M_{10}$  high through the  $M_8$ –

$M_9$  inverter, causing the ML to discharge. In case of a match (stored '1'),  $MTJ_1 = LRS$  while  $MTJ_4 = HRS$ , causing node  $Q_B$  to discharge faster, and driving  $Q$  to  $V_{DD}$ . The input of  $M_{10}$  is low, disconnecting the ML path to ground.

Finally, for a search 'X' operation  $S_L = 0$ , and  $S_{LN} = 0$ , and no discharge paths are enabled. Both nodes  $Q$  and  $Q_B$  remain at  $V_{DD}$ , and the result is always a match.

Table. 4.4 summarizes the search-line, word-line and bit-line input combinations for each search operation, as well as the matchline response depending on the stored data. The search time is given by ML discharge delay, which depends on the load capacitance and hence on the number of parallel connected cells (word-length).

Table 4.4: Search Operations for the proposed 17T4MTJ NV-CAM cell

| Operation  | Signals  |          |       |          |          |          | Stored Data    |         | Matchline <sup>‡</sup> |

|------------|----------|----------|-------|----------|----------|----------|----------------|---------|------------------------|

|            | $S_L$    | $S_{LN}$ | $B_L$ | $B_{LN}$ | $W_{L0}$ | $W_{L1}$ | Value          | States* |                        |

| Search '0' | 0        | $V_{DD}$ | 0     | 0        | 0        | 0        | '0'            | H,L,H,L | Match                  |

|            | 0        | $V_{DD}$ | 0     | 0        | 0        | 0        | '1'            | L,H,L,H | Mismatch               |

| Search '1' | $V_{DD}$ | 0        | 0     | 0        | 0        | 0        | '0'            | H,L,H,L | Match                  |

|            | $V_{DD}$ | 0        | 0     | 0        | 0        | 0        | '1'            | L,H,L,H | Mismatch               |

| Search 'X' | 0        | 0        | 0     | 0        | 0        | 0        | - <sup>†</sup> | -       | Match                  |

\* HRS and LRS states are abbreviated as H and L. Each letter corresponds to  $MTJ_{1,2,3,4}$  respectively.

<sup>†</sup> Search 'X' behaves equally for any stored data.

<sup>‡</sup> Matchline evaluation has  $< 1\text{ns}$  delay.

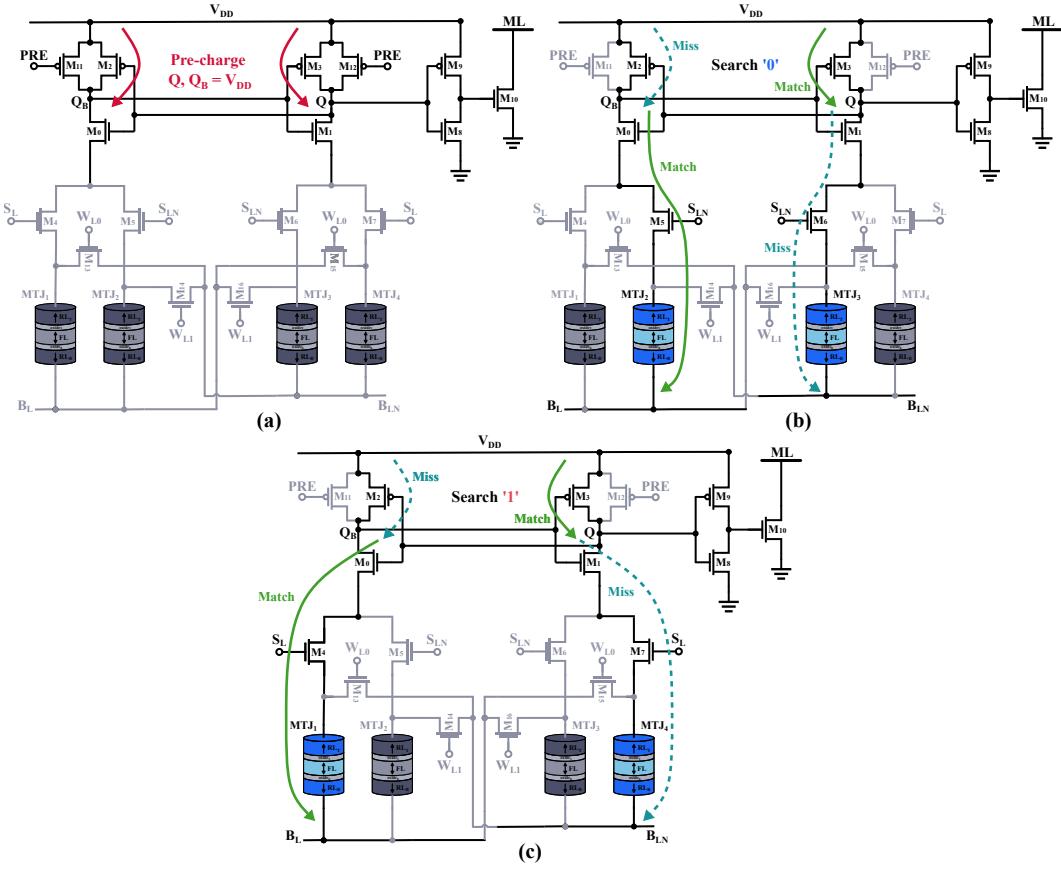

### 4.3 Performance Analysis

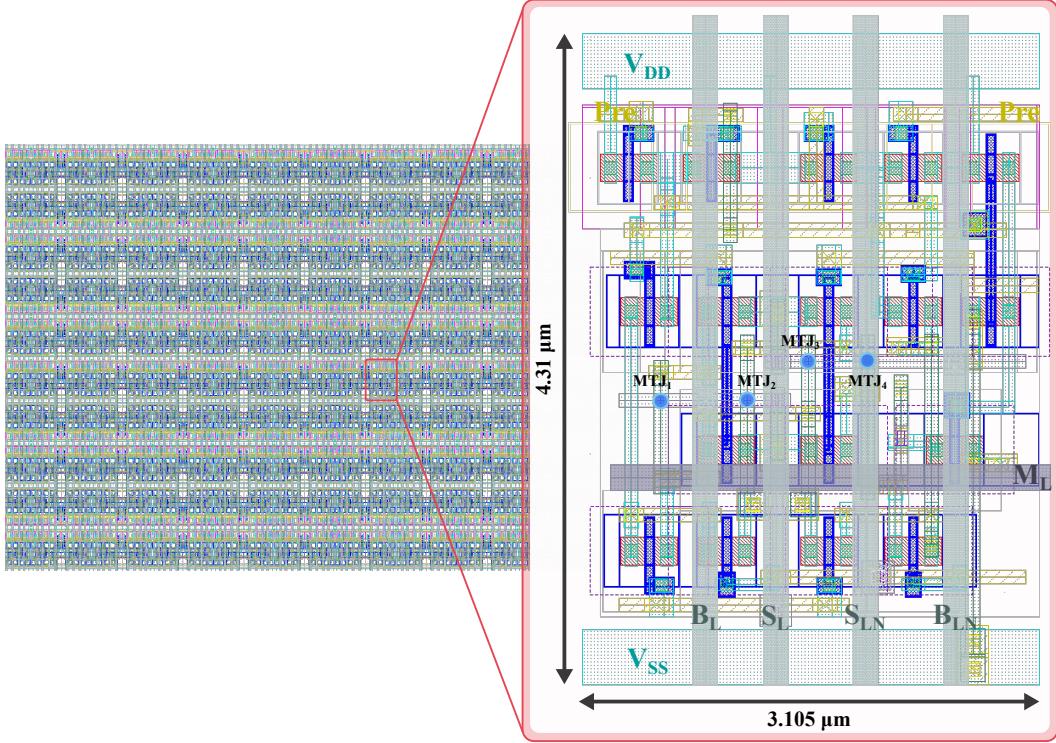

Fig. 4.6 shows the proposed 17T4MTJ cell layout implemented using transistors in the TSMC 65nm technology node. All transistors are standard-size transistors with width  $w = 200\text{nm}$  and length  $l = 60\text{nm}$ . The cell has a total width of  $3.105\mu\text{m}$ , and a height of  $4.31\mu\text{m}$ , giving a total area of  $13.38\mu\text{m}^2$ . The use of standard-sized transistors allows for a compact cell design, even with the high transistor count. Note that the proposed NV-CAM cell presents

a larger area footprint as compared to other NV-CAM designs. However, this overhead becomes less significant when amortized over a large area available to design the memory macro. For example in 3D integration applications, an entire tier can be dedicated to the NV-CAM.

Figure 4.6: Cell layout for the proposed 17T4MTJ NV-CAM cell with a total area footprint of  $13.38\mu\text{m}^2$ .

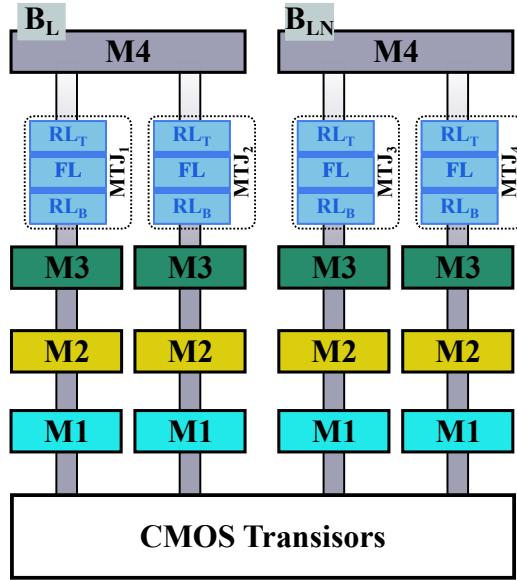

Integration with non-volatile devices can be realized using a hybrid CMOS/MTJ process where DMTJ devices are fabricated between Metal-3 (M3) and Metal-4 (M4) during the back-end of the CMOS process [55]. Fig. 4.7 shows a 3D hybrid process scheme.

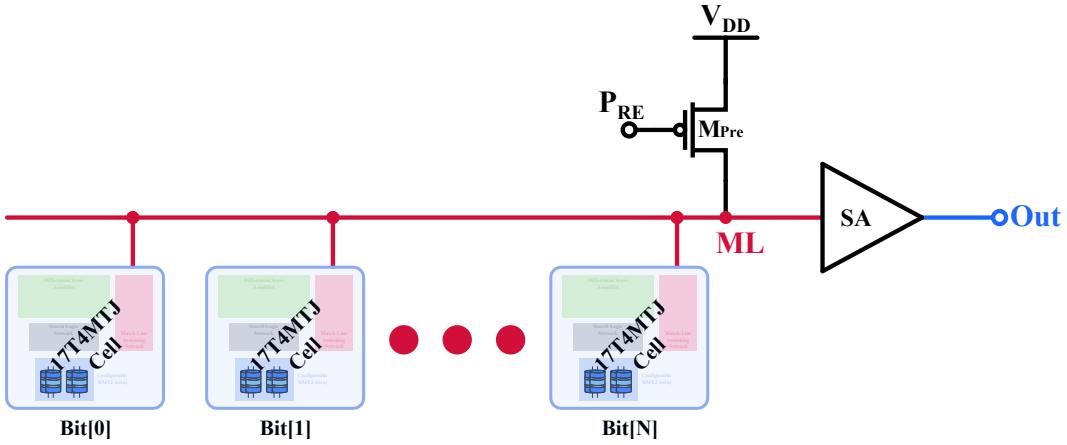

The performance of the 17T4MTJ cell is examined using Monte-Carlo simulations with 1000 runs for every measurement. Results are obtained from the  $3\sigma$  corners to examine the effects of process variations on DMTJ devices and CMOS transistors. The performance of the NV-CAM cell is tested on different memory word lengths ranging from 8- to 128-cells. Fig. 4.8 shows the CAM word setup, consisting of an array of  $n$ -cells connected to a matchline using the NOR topology. The matchline is connected to a transistor  $M_{Pre}$  of dimensions  $w = 1\mu\text{m}$ ,  $l = 60\text{nm}$  that is used during the pre-charge phase. The

Figure 4.7: Hybrid 3D CMOS/MTJ process. DMTJs are placed between M3 and M4 [55].

sense amplifier consists of an unskewed buffer that drives the word output. Measurements are done for  $V_{DD} = 1V$  and  $V_{DD} = 1.2V$ .

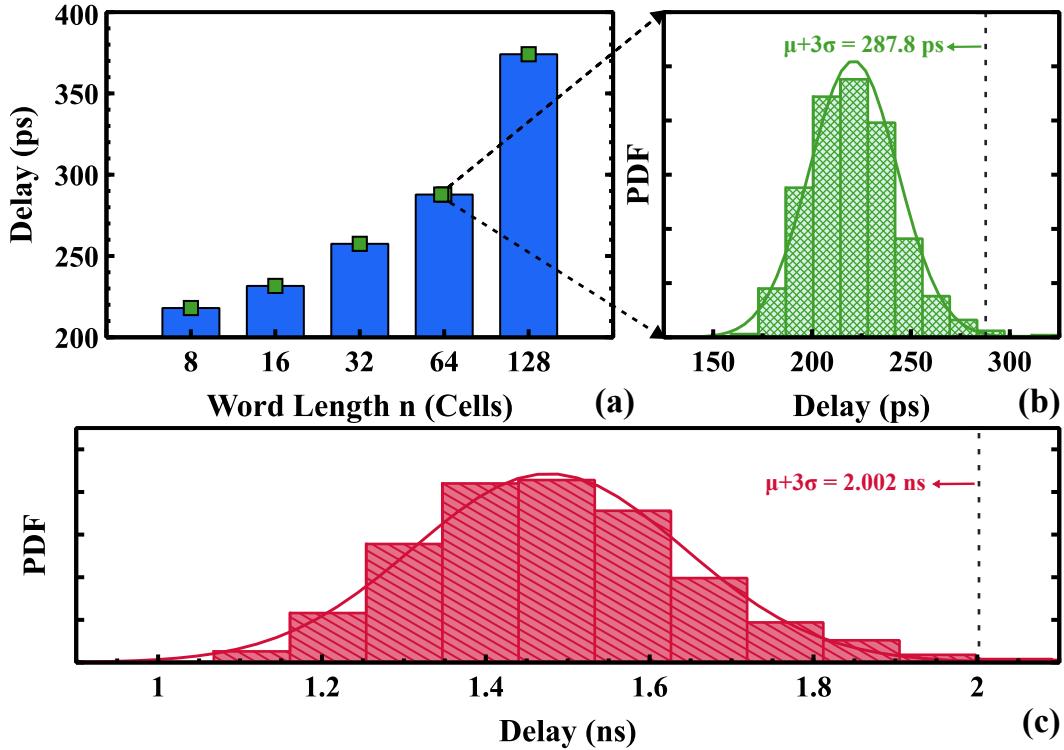

Table. 4.4 shows the search results at the  $3\sigma$  corner for both values of  $V_{DD}$  at every word length. The search latency is defined as the 50% delay between the rise of  $PRE$  (end of the pre-charge phase), and the fall of  $Out$ , signaling a mismatch. The delay is measured for the worst-case scenario, where there is only a single bit mismatch between the stored word and the search word. For  $V_{DD} = 1V$ , Fig. 4.9 (a) shows the search latency ( $t_{search}$ ) as a function of word length for the  $3\sigma$  corner. The average search time is  $274ps$ , and the latency is kept below  $0.5ns$  for every length. Fig. 4.9 (b) shows the probability density function (PDF) for a 64-bit word. Using  $V_{DD} = 1.2V$ , the average latency is  $196ps$ , corresponding to a  $1.4\times$  improvement in performance. For a 64-bit word in particular, the search at a higher  $V_{DD}$  is  $1.35\times$  times faster.

The design has a very low SER, with the value rising with word length from 0% up to 0.2% when  $V_{DD} = 1V$ . The SER does not seem to increase beyond the 16-bit length, suggesting that a greater number of Monte-Carlo simulations are required to properly determine a trend. In the case that an application requires an even lower SER, [56] includes guidelines on improving the error rates by

Figure 4.8: 64-bit CAM word using the proposed 17T4MTJ NV-CAM cell. The NOR matchline structure is pre-charged using transistor  $M_{Pre}$ . The sense amplifier is implemented by a simple static buffer.

increasing the device TMR, and adjusting the sizes of transistors  $M_8, M_9$  in the ML switching network, as well as the transistors in the search logic network. Increasing the value of  $V_{DD}$  has a detrimental effect on the SER, causing it to rise to a maximum of 0.9% for the 128-bit word. The cause for this increase in errors is due inverse relation between the applied device voltage and the TMR, which is captured by the DMTJ compact model. For high voltages, the resistance of the HRS and LRS states can become practically equal. Therefore, increasing  $V_{DD}$  improves the response time of the latch, but also reduces the minimum sensing margin between MTJ states which translates to a greater number of errors when process variations are taken into account.

In typical applications, the mismatch case is more energy-expensive and much more common than the match case. However, for the proposed application, each row would be part of a processing unit (PU) which will match at least once for every processed bit, therefore; a significant number of matches are expected during every search. The search energy is reported here as the average between match and mismatch during the evaluation phase. For  $V_{DD} = 1V$ , the maximum evaluation energy is  $263.1fJ$  for the 128-bit word. A 64-bit word consumes 50.96% less energy ( $129.05pJ$ ), as expected.

The average energy consumption during the pre-charge phase is around 71% of the evaluation energy for every word length. In this phase, a significant amount

Figure 4.9: Performance evaluation results for the proposed 17T4MTJ NV-CAM cell after 1000 Monte-Carlo runs. (a) Search latency as a function of word length at the  $3\sigma$  corner. (b) PDF of search delay for a 64-bit word. (c) PDF of the worst-case write latency for a single phase.

of energy is consumed by the dynamic latch. For a 64-bit word, only  $13.3pJ$  are spent in charging the ML, while the NOR cell array requires  $85.26pJ$ . Methods like ML segmentation can be used to reduce the number of pre-charged cells and provide a better energy efficiency for the CAM array, albeit at an increased latency. The average search energy of a 64-bit word considering both pre-charge and evaluation phases is  $221.0pJ$ .

For  $V_{DD} = 1.2V$ , the maximum evaluation energy is  $387.45fJ$ . The average energy consumption of 64-bit word on both phases is  $332pJ$ .

Right at the start of the evaluation phase, the nodes  $Q$  and  $Q_B$  are discharged through the active MTJs in the MAB. In that moment a short, but high transient current flows from  $V_{DD}$  to  $B_L$  and  $B_{LN}$  through the DMTJs. From transient simulations with  $V_{DD} = 1.2V$ , the current pulse reaches a peak of  $3.55 \times I_{C0}$ . Since the read and write paths on the two terminal device are

shared, there is a risk of overwriting stored data during search. The probability of switching depends not only on the current strength, but also on the length of the pulse. If the pulse is short enough, the switching probability can be made negligible  $p_{switch} = 10^{-7}$ , corresponding to a WER of  $1 - 10^{-7}$ . The transient pulse duration was measured in 1000 Monte-Carlo simulations with  $V_{DD} = 1.2V$ . The average pulse length is  $0.125ns$ . Meanwhile, the average switching time (WER = 0.999999) is  $0.221ns$ . Pulses with higher currents discharge the internal nodes faster, which leads to shorter transients, while longer pulses produce lower currents. From all the simulations, there were no instances where the pulse length exceeded the switching time, ensuring data reliability during search operations. None of the SER errors were caused by data overwrite.

Table 4.5: Search performance for the proposed 17T4MTJ NV-CAM cell

| $V_{DD}$ (V) | Word-Length n | Search Time (ps) | Eval. Energy (fJ) | SER % |

|--------------|---------------|------------------|-------------------|-------|

| 1            | 8             | 218.00           | 19.19             | 0.0%  |

|              | 16            | 231.56           | 34.79             | 0.2%  |

|              | 32            | 257.52           | 66.16             | 0.2%  |

|              | 64            | 287.79           | 129.05            | 0.2%  |

|              | 128           | 374.12           | 263.15            | 0.2%  |

| 1.2          | 8             | 156.40           | 27.31             | 0.0%  |

|              | 16            | 165.28           | 50.33             | 0.3%  |

|              | 32            | 182.44           | 97.14             | 0.3%  |

|              | 64            | 211.97           | 191.65            | 0.4%  |

|              | 128           | 265.43           | 387.45            | 0.9%  |

Table. 4.3 shows the write results at the  $3\sigma$  corner for both values of  $V_{DD}$ . The single phase write time  $t_{phase}$  is defined as the switching delay between the rise of  $W_0$  for phase 1, or  $W_{L1}$  for phase 2, and the change of state in the DMTJs. The write path consists of a 1T1MTJ structure, which enables fast writing with standard-sized transistors, and without the need for a high write voltage.

The transition from LRS $\rightarrow$ HRS is always the slowest since the nMOS access transistor is connected to  $V_{DD}$ . For example, during phase 1 of the Write '0' operation,  $B_{LN} = V_{DD}$  and transistor  $M_{13}$  causes a drop in the voltage going

into  $MTJ_1$ , reducing the switching current. Fig. 4.9 (c) shows the PDF for the worst-case write delay in a single phase when  $V_{DD} = 1V$ . The single phase write delay is  $t_{phase} = 2.002ns$ , giving a total  $t_{write} = 4.004ns$ . The write energy is  $241pJ$ . On the other hand, the write performance can improve when using a higher supply voltage. For  $V_{DD} = 1.2V$  the cell is  $1.6\times$  faster, with  $t_{write} = 2.468ns$ . Although the power consumption during write increases, the write energy improves by 3.5% due to the shorter delay.

Table 4.6: Write performance for the proposed 17T4MTJ NV-CAM cell

| $V_{DD}$ (V) | Single Phase     | Total            | Total             |

|--------------|------------------|------------------|-------------------|

|              | Write Delay (ns) | Write Delay (ns) | Write Energy (fJ) |

| 1            | 2.002            | 4.003            | 241               |

| 1.2          | 1.234            | 2.468            | 230.3             |